©Copyright 2013

Brandon Lucia

## System Support for Concurrent Software Reliability

Brandon Lucia

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

University of Washington

2013

Reading Committee:

Luis Ceze, Chair

Mark Oskin

Daniel Grossman

Program Authorized to Offer Degree: Department of Computer Science and Engineering

#### **Abstract**

System Support for Concurrent Software Reliability

Brandon Lucia

Chair of the Supervisory Committee:

Associate Professor Luis Ceze Computer Science and Engineering

Parallel and concurrent software is more complex than sequential software because interactions between concurrent computations and the ordering of program events can vary across executions. This nondeterministic variation is hard to understand and control, introducing the potential for concurrency bugs. This dissertation addresses two challenges related to concurrency bugs, focusing on shared-memory multi-threaded programs. First, concurrency bugs are hard to find, understand, and fix, but debugging is essential to software correctness. Second, concurrency bugs cause schedule-dependent failures that degrade system reliability.

We develop two new concurrency debugging techniques based on statistical analysis and novel abstractions of inter-thread communication. These techniques isolate communications related to bugs and reconstruct failing executions. We show several hardware and software system designs that efficiently implement these techniques. We also develop two techniques for automatically avoiding schedule-dependent failures due to atomicity violations, a common concurrent program failure. We use specialized serializability analyses to identify code that should be atomic and system support to enforce atomicity. We implement these techniques with architecture and system support. Finally, we develop a mechanism for general schedule-dependent failure avoidance. We use a statistical analysis and leverage large communities of deployed systems to learn how to constrain executions to avoid previously seen failures. We show a software-only distributed system implementation that avoids real software failures with overheads low enough for production use.

## **TABLE OF CONTENTS**

|           | I                                                                     | Page |

|-----------|-----------------------------------------------------------------------|------|

| List of I | Figures                                                               | iii  |

| List of T | Tables                                                                | vii  |

| Chapter   | 1: The Concurrent Software Reliability Problem                        | 1    |

| 1.1       | Concurrency and Parallelism in Shared-memory Multi-threaded Programs  | 3    |

| 1.2       | Concurrency Bugs and Schedule-Dependent Failures                      | 7    |

| 1.3       | Challenges Addressed by this work                                     | 13   |

| 1.4       | Contributions                                                         | 17   |

| Chapter   | 2: Bugaboo: Debugging with Context-Aware Communication Graphs         | 21   |

| 2.1       | Context-Aware Communication Graphs                                    | 22   |

| 2.2       | Implementing Context-Aware Communication Graph Collection             | 28   |

| 2.3       | Debugging with Context-Aware Communication Graphs                     | 30   |

| 2.4       | Evaluation                                                            | 31   |

| 2.5       | Conclusions, Insights, and Opportunities                              | 38   |

| Chapter   | Recon: Debugging with Reconstructed Execution Fragments               | 41   |

| 3.1       | Reconstructed Execution Fragments                                     | 43   |

| 3.2       | Debugging with Reconstructions                                        | 50   |

| 3.3       | Implementation                                                        | 55   |

| 3.4       | Evaluation                                                            | 59   |

| 3.5       | Conclusions, Insights, and Opportunities                              | 66   |

| Chapter   | 4: Architecture Support for Context-Aware Communication Graphs        | 68   |

| 4.1       | CACG-HW: Architectural Support for Context-Aware Communication Graphs | s 69 |

| 4.2       | Evaluation                                                            | 73   |

| 4.3       | Conclusions, Insights, and Opportunities                              | 77   |

| Chapter  | 5: Atom-Aid: Avoiding Atomicity Violations                                                                |

|----------|-----------------------------------------------------------------------------------------------------------|

| 5.1      | Background on Implicit Atomicity                                                                          |

| 5.2      | Implicit Atomicity Hides Atomicity Violations                                                             |

| 5.3      | Actively Hiding Atomicity Violations                                                                      |

| 5.4      | Design Overview                                                                                           |

| 5.5      | $ \label{thm:limit}  \mbox{Implementing Atom-Aid with Implicit Atomicity and Hardware Signatures}  .  93$ |

| 5.6      | Evaluation                                                                                                |

| 5.7      | Conclusions, Insights, and Opportunities                                                                  |

| Chapter  | 6: ColorSafe: Avoiding Multi-variable Atomicity Violations 107                                            |

| 6.1      | Multi-variable Atomicity Violations and Serializability                                                   |

| 6.2      | Color<br>Safe: Detecting and Avoiding Multi-Variable Atomicity Violations $$ 110                          |

| 6.3      | Architectural Support                                                                                     |

| 6.4      | Debugging with ColorSafe                                                                                  |

| 6.5      | Evaluating ColorSafe                                                                                      |

| 6.6      | Conclusions, Insights, and Opportunities                                                                  |

| Chapter  | 7: Aviso: Avoiding Schedule-Dependent Failures                                                            |

| 7.1      | Schedule-Dependent Failures                                                                               |

| 7.2      | System Overview                                                                                           |

| 7.3      | Monitoring Events and Failures                                                                            |

| 7.4      | Generating Constraints and Avoiding Failures                                                              |

| 7.5      | Selecting and Distributing Constraints                                                                    |

| 7.6      | System Implementation                                                                                     |

| 7.7      | Evaluation                                                                                                |

| 7.8      | Conclusions, Insights, and Opportunities                                                                  |

| Chapter  | 8: Related Work                                                                                           |

| 8.1      | Debugging Concurrency Errors                                                                              |

| 8.2      | Avoiding Schedule-Dependent Failures                                                                      |

| Chapter  | 9: Conclusions                                                                                            |

| 9.1      | Cross-cutting Themes                                                                                      |

| 9.2      | Final Thoughts                                                                                            |

| Bibliogr | anhy 205                                                                                                  |

## **LIST OF FIGURES**

| Figure | Number                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

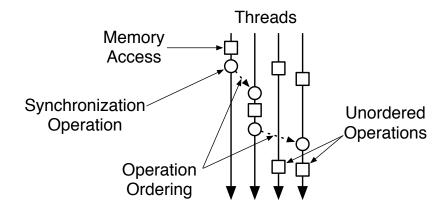

| 1.1    | An illustration of a shared memory multi-threaded program execution. The threads execute memory accesses (squares) that can read and write values to a shared memory space. Each thread executes its operations sequentially, but different threads' operations are independent and unordered by default. Threads can use synchronization operations (circles) to impose an ordering on operations in different threads that would otherwise be unordered. | . 4  |

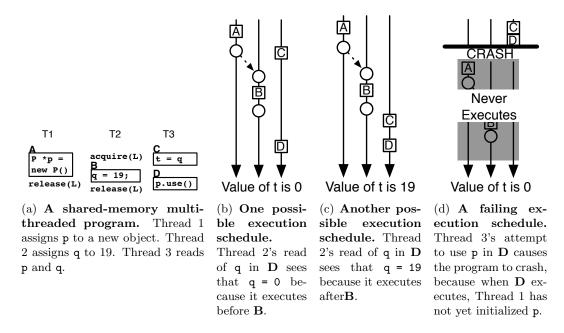

| 1.2    | Different executions of a shared-memory multi-threaded program .                                                                                                                                                                                                                                                                                                                                                                                           | 6    |

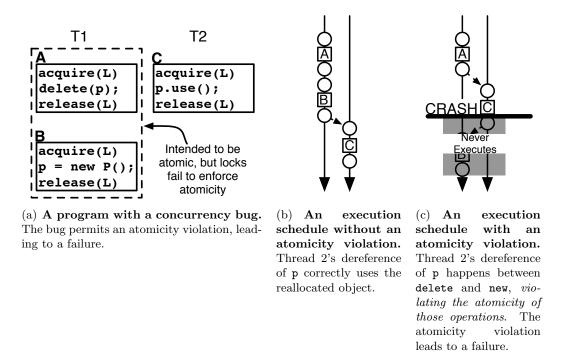

| 1.3    | Code with a concurrency bug that can lead to an atomicity violation failure.                                                                                                                                                                                                                                                                                                                                                                               | 10   |

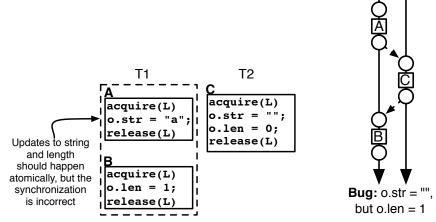

| 1.4    | A concurrency bug involving multiple related variables that can lead to an atomicity violation.                                                                                                                                                                                                                                                                                                                                                            | 12   |

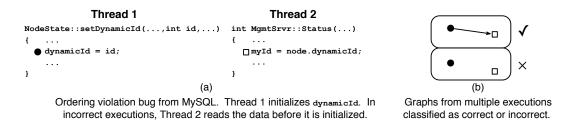

| 2.1    | High-level view of how communication graph structure can reveal a failure. Markers represent memory operations involving shared data                                                                                                                                                                                                                                                                                                                       | 23   |

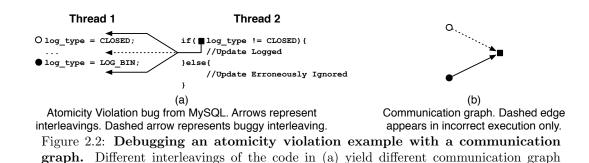

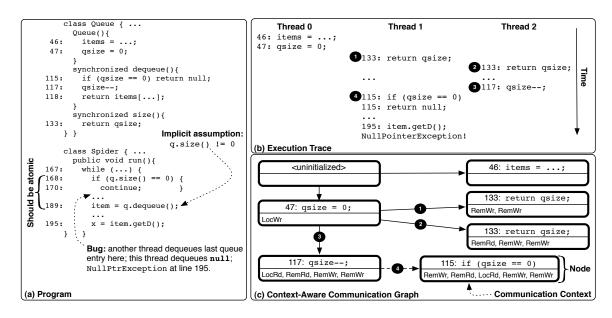

| 2.2    | Debugging an atomicity violation example with a communication graph. Different interleavings of the code in (a) yield different communication graph edges in (b)                                                                                                                                                                                                                                                                                           | 24   |

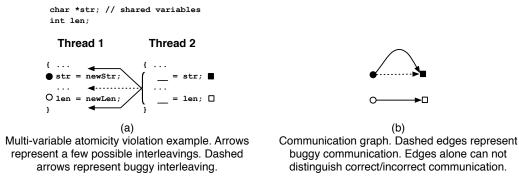

| 2.3    | A basic communication graph is often insufficient for debugging. Comparing edge sets from failing and non-failing executions' graph does reveal the cause of the failure.                                                                                                                                                                                                                                                                                  | 25   |

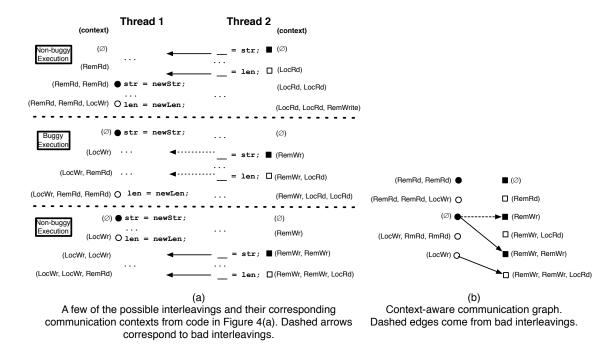

| 2.4    | A context-aware graph reveals the cause of a multi-variable atomicity violation. Different executions produce different sets of communication graph edges. Using a context-aware graph, edge differences reveal the communication responsible for the failure. Using a context-oblivious graph, it does <i>not</i>                                                                                                                                         | 29   |

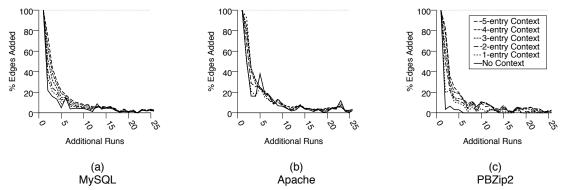

| 2.5    | <b>Graph convergence.</b> Graphs reach a convergent structure with an increasing number of executions' graphs. The figure shows MySQL (a), Apache (b), and PBZip2 (c)                                                                                                                                                                                                                                                                                      | 36   |

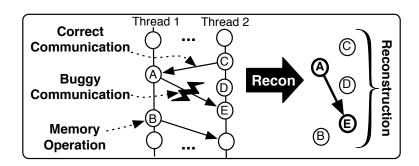

| 3.1    | Recon reconstructs fragments of program execution                                                                                                                                                                                                                                                                                                                                                                                                          | 41   |

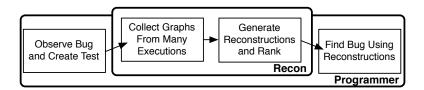

| 3.2    | Overview of Recon's operation.                                                                                                                                                                                                                                                                                                                                                                                                                             | 42   |

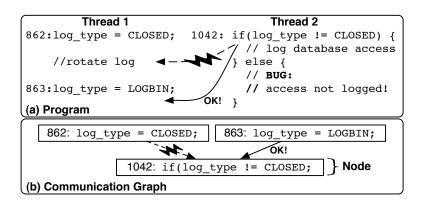

| 3.3    | A buggy program and communication graph. The dashed graph edge represents the buggy communication                                                                                                                                                                                                                                                                                                                                                          | 44   |

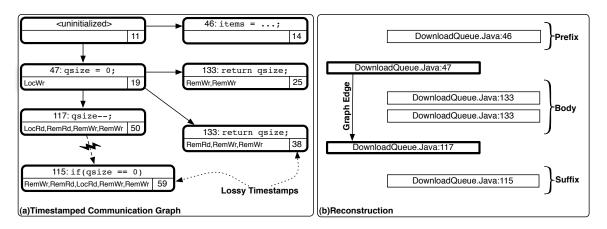

| 3.4 | A buggy program, a failing execution schedule, and its context-aware communication graph. Nodes represent the execution of operations in a specific context. Edges represent communication between nodes. Note that we only include events in nodes' contexts that appear in our abbreviated trace for simplicity's sake | 45       |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.5 | A timestamped communication graph and corresponding reconstruction. The graph and reconstruction are based on the program, execution schedule, and graph in Figure 3.4                                                                                                                                                   | 47       |

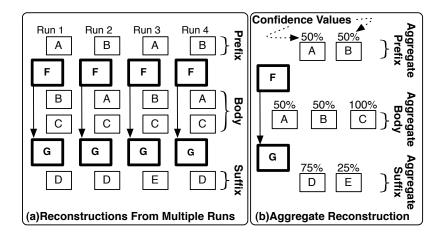

| 3.6 | <b>Aggregating reconstructions from many executions.</b> (a) shows reconstructions of many different failing program executions. (b) shows the resulting aggregate reconstruction with confidence values                                                                                                                 | 50       |

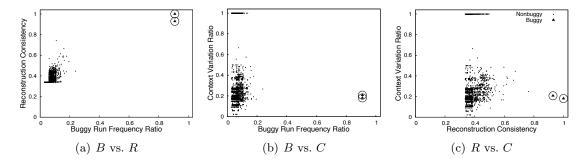

| 3.7 | Pair-wise feature plots illustrating class separation. The plots show how effectively each pair of features separate reconstructions of the failure from others for apache. We only show the top 2000 ranked reconstructions and points representing reconstructions of the failure are circled                          | 54       |

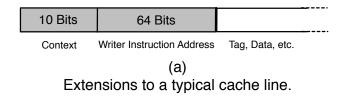

| 4.1 | CACG-HW architectural extensions to a typical multiprocessor.  New architectural components are shaded                                                                                                                                                                                                                   | 70       |

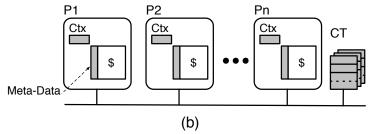

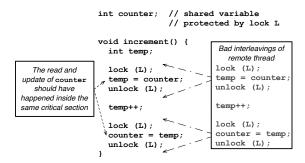

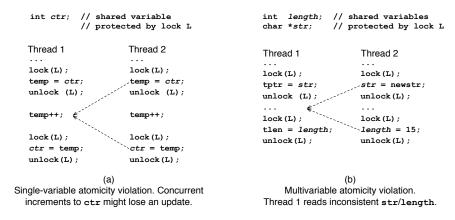

| 5.1 | A simple example of an atomicity violation. The read and update of counter from two threads may interleave such that the counter is incremented only once.                                                                                                                                                               | 80       |

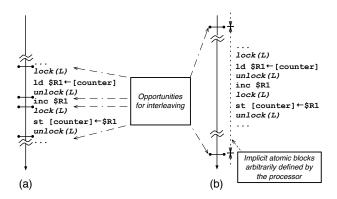

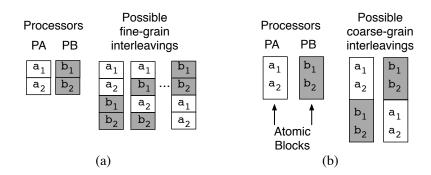

| 5.2 | <b>Opportunities for interleaving.</b> (a) shows where interleaving from other threads can happen in a traditional system. (b) shows where such interleavings can happen in systems that provide implicit atomicity                                                                                                      | 81       |

| 5.3 | Fine- (a) and coarse-grained (b) access interleaving. There are six possible interleavings for the fine-grained system and two possible interleavings for the coarse-grained system                                                                                                                                      | 83       |

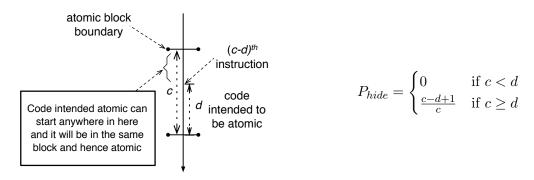

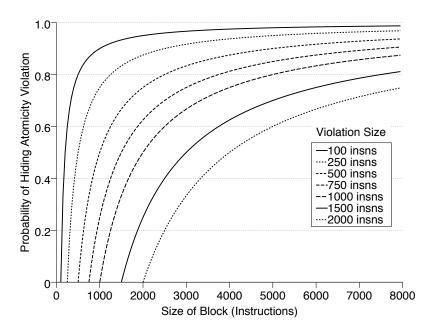

| 5.4 | Naturally hiding an atomicity violation. The figure shows the boundaries of a sequence of instructions intended to be atomic within dynamic atomic block boundaries. $P_{hide}$ is the probability that the entire sequence                                                                                              | 0.5      |

| 5.5 | executes within the block.  Probability of hiding atomicity violations as a function of dynamic atomic block size.                                                                                                                                                                                                       | 85<br>86 |

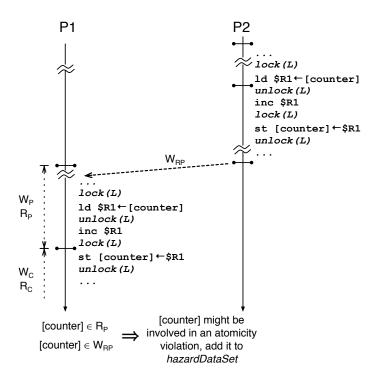

| 5.6 | Identifying data involved in a potential atomicity violation. Atom-Aid discovers that counter might be involved in an atomicity violation and adds it to the <i>hazardDataSet</i>                                                                                                                                        | 90       |

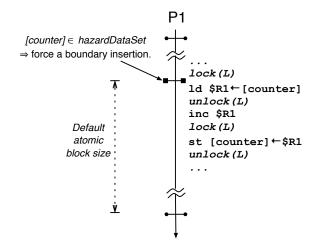

| 5.7 | Actively hiding an atomicity violation. When counter is accessed, a block boundary is inserted automatically because counter belongs to the hazardDataSet.                                                                                                                                                               | 91       |

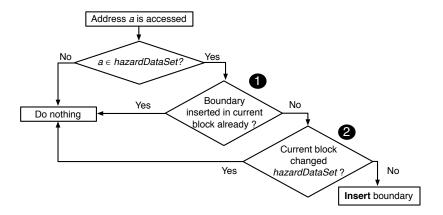

| 5.8  | Block boundary insertion logic. Flowchart showing Atom-Aid's policy for inserting dynamic atomic block boundaries                                                                                                                                                                                                                                                                                                                                                                              |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

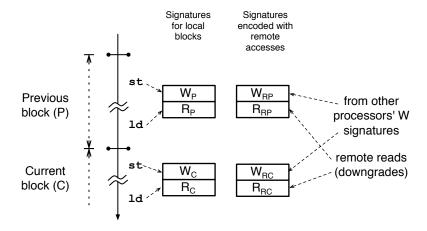

| 5.9  | Signatures used by Atom-Aid to detect likely atomicity violations. 94                                                                                                                                                                                                                                                                                                                                                                                                                          |

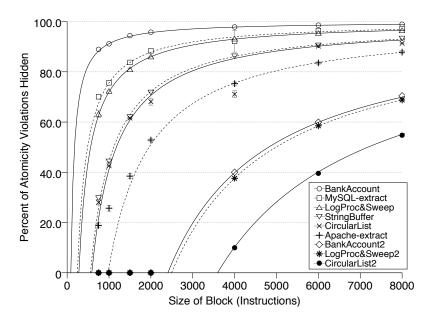

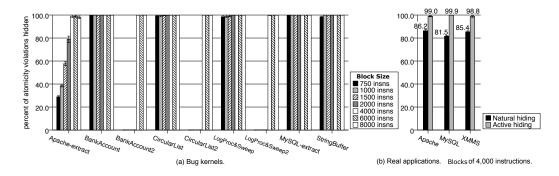

| 5.10 | Empirically evaluating natural hiding. Experimental data on the natural hiding of atomicity violations with implicit atomicity for various block sizes and bug kernels. Points show empirical data, curves show data predicted by our analytical model $(P_{hide})$                                                                                                                                                                                                                            |

| 5.11 | Atomicity violations hidden by Atom-Aid. Results are averaged over all trials and error bars show the $95\%$ confidence interval                                                                                                                                                                                                                                                                                                                                                               |

| 6.1  | <b>Example atomicity violations.</b> (a) shows a single-variable violation and (b) shows a multi-variable violation. The example in (b) was distilled from https://bugzilla.mozilla.org/show_bug.cgi?id=73291                                                                                                                                                                                                                                                                                  |

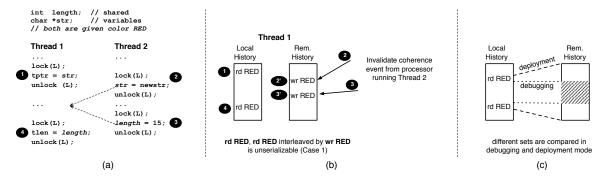

| 6.2  | Unserializable color access interleavings                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.3  | Example of a unserializable color interleaving. The example corresponds to case 5 in Table 6.2. str and length are left mutually inconsistent. 111                                                                                                                                                                                                                                                                                                                                             |

| 6.4  | Overview of how ColorSafe detects multi-variable atomicity violations. The numbers in the dark circles denote the order of events happening simultaneously in (a) and (b)                                                                                                                                                                                                                                                                                                                      |

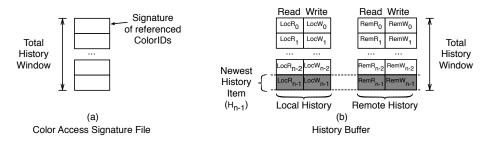

| 6.5  | Keeping color access history                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

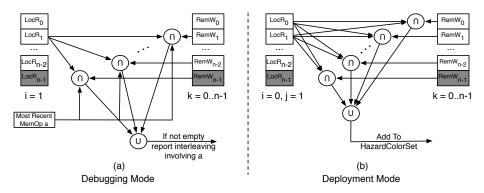

| 6.6  | Detecting unserializable interleavings in (a) debugging mode and (b) deployment mode. In (a), only actual interleavings are being considered for the serializability test: the current access to $a$ , the local history item $i$ and the remote history items with $k \geq i$ . In (b), all items in the remote history are being considered for the serializability test: local history item $i$ , followed by local history item $j$ , and all possible remote history items $(k = 0n - 1)$ |

| 6.7  | Violations avoided in bug kernels and full applications. Results are shown for experiments using manual and malloc data coloring. †We used a different system configuration for MySQL. We explain the details in Section 6.5.2 (Difficulties with MySQL)                                                                                                                                                                                                                                       |

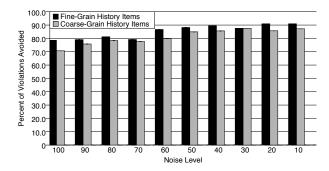

| 6.8  | Impact of history item granularity on violation avoidance. The plot shows the number of atomicity violations avoided in kernel NetIO under synthetic noise for fine- and coarse-grain history items with a constant history window                                                                                                                                                                                                                                                             |

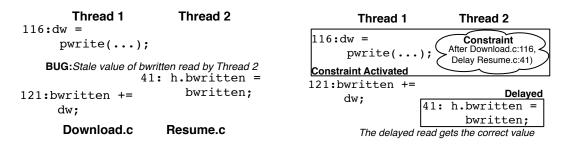

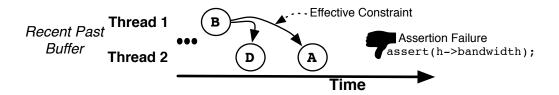

| 7.1  | A schedule-dependent failure in AGet-0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7.2  | The Avoidance-Testing Duality                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

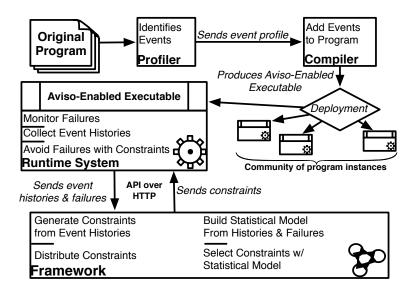

| 7.3         | Aviso's components. The compiler and profiler find and instrument events. The runtime system monitors events and failures and avoids events. The framework generates constraints, selects likely effective constraints using a statistical model, and shares effective constraints in a community of software                                                                                                                                                                                                                                                                                       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

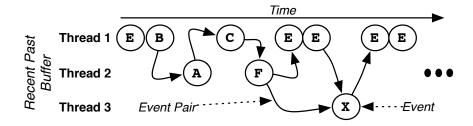

| 7.4         | Enumerating pairs from a failing execution's RPB. There are three threads, and time proceeds left to right. Circles are events, and arcs between events are event pairs. Arcs for duplicate pairs are omitted. The figure shows a single 10-event window of events, but selection occurs for all 10-event windows. 144                                                                                                                                                                                                                                                                              |

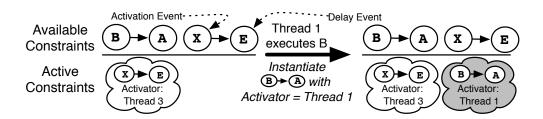

| 7.5         | Constraint Activation. Available constraints are those that Aviso has made available to the execution. Active constraints are constraint instances that have been instantiated and can trigger delays. The large, central arrow signifies Thread 1 executing event B. To the left of the arrow there are no instances of the constraint $(B, A)$ ; event B is its activation event, so when B is executed an instance of the constraint is added to the Active Constraints set (shaded cloud). Aviso records that Thread 1 is the instance's activator in the instance                              |

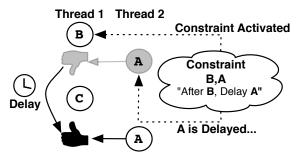

| 7.6         | How a constraint avoids a failure. The constraint is shown in the cloud and is made from events $B$ and $A$ ; when a thread executes $B$ , the constraint is instantiated. When another thread executes $A$ , it is delayed. The left side shows an execution snippet that can be viewed as both an atomicity violation and an ordering violation                                                                                                                                                                                                                                                   |

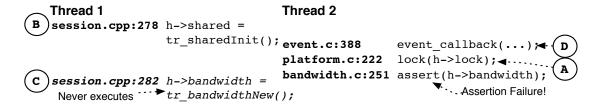

| 7.7         | A use-before-initialization failure from Transmission and the constraint that avoids it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

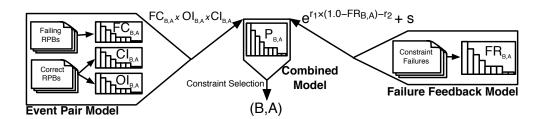

| 7.8         | Aviso's statistical model. The event pair model tracks feature values for each constraint. The failure feedback model tracks constraints' failure rates. The combined model is comprised of the other two, yielding a selection probability for each constraint                                                                                                                                                                                                                                                                                                                                     |

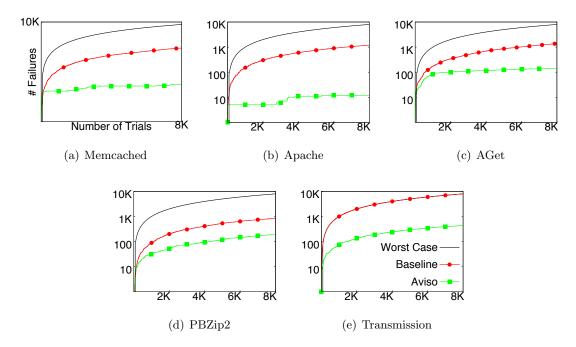

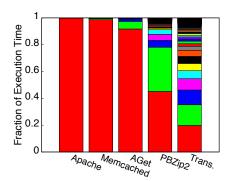

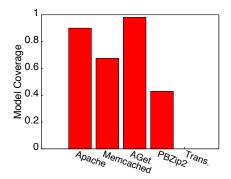

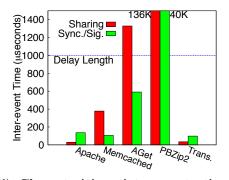

| 7.9         | Aviso's improvement in reliability. We show data for (a)Memcached, (b)Apache, (c)AGet, (d)PBZip2, and (e)Transmission. The x-axis shows execution time in number of trials – logical time ticks for servers, executions for standalone applications. We ran each program for 8000 trials. The y-axis shows the number of failures that have occurred at a given point in time on a log scale. The top (black) curve shows the worst case: every execution is a failure. The middle (red) curve shows the reliability of the baseline, compiled and run completely without Aviso. The bottom (green) |

| <b>7</b> 10 | curve shows the reliability with Aviso                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

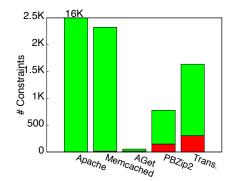

| 7.10        | Characterizing Aviso's behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## **LIST OF TABLES**

| Table I | Number                                                                                                                                                                                                                                                                                                                                                                    | Page |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1     | <b>Bug workloads used to evaluate Bugaboo.</b> AV indicates an Atomicity Violation, OV indicates an Ordering Violation, and MVAV indicates Multi-Variable Atomicity Violation                                                                                                                                                                                             | . 32 |

| 2.2     | Bug detection accuracy using Bugaboo. We report the number of code point inspections required before the corresponding bug was found, the number in parenthesis show the number of distinct functions. Note that one inspection indicates that zero irrelevant code points needed inspection, since the bug was found on the first. Results are averaged over five trials | . 33 |

| 2.3     | Debugging effectiveness for BB-SW (word) with different context sizes. Dash (—) indicates the bug was not found with the corresponding context size                                                                                                                                                                                                                       | . 35 |

| 2.4     | Characterization of BB-SW and communication graphs sizes                                                                                                                                                                                                                                                                                                                  | . 37 |

| 3.1     | Effectiveness of features. The table shows the reliefF rank of each feature for our C/C++ benchmark programs                                                                                                                                                                                                                                                              | . 55 |

| 3.2     | <b>Buggy programs used to evaluate Recon.</b> We used both C/C++ programs and Java programs and we included a variety of bug types                                                                                                                                                                                                                                        | . 60 |

| 3.3     | Properties of reconstructions for our benchmarks                                                                                                                                                                                                                                                                                                                          | . 61 |

| 3.4     | <b>Performance of Recon.</b> We shows Recon's base configuration and many less-optimized configurations relative to uninstrumented execution                                                                                                                                                                                                                              | . 64 |

| 4.1     | Bug detection accuracy using CACG-HW. We report the number of code point inspections required before the corresponding bug was found. The number in parenthesis show the number of distinct functions. Note that one inspection indicates that zero irrelevant code points needed inspection, since the bug was found on the first. Results are averaged over five trials | . 74 |

| 4.2     | Imprecision for different configurations of CACG-HW. We show imprecision for line-level and cache-to-cache-only tracking of inter-thread communication.                                                                                                                                                                                                                   | . 75 |

| 4.3     | Characterization of CACG-HW                                                                                                                                                                                                                                                                                                                                               |      |

| 5.1     | Serializability analysis. The table shows the analysis and interpretation of each interleaving described in [80].                                                                                                                                                                                                                                                         | . 88 |

| 5.2 | Cases when an address is added to the hazardDataSet 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.3 | Bug benchmarks used to evaluate Atom-Aid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.4 | Characterizing Atom-Aid. The table shows data for both the signature and non-signature implementations                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.5 | Characterization of the bug detection process for real applications using Atom-Aid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.1 | Bugs used to evaluate ColorSafe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.2 | Characterization of Ephemeral Transactions. The rate of ET starts, % of useful ETs, and % of conflicting useless ETs for full applications in deployment mode. Ap2.0 and MySQL were run using malloc coloring, and AGet, manual coloring. MySQL was run with the modified configuration described in Section 6.5.2 (Difficulties with MySQL)                                                                                                                                                                                                                               |

| 6.3 | Failure avoidance for a variety of ET sizes. Applications marked with a <sup>m</sup> were run using manual coloring, because their bugs involve global and heap variables; All others were run with malloc-coloring                                                                                                                                                                                                                                                                                                                                                        |

| 6.4 | Impact of noise on ET usefulness. Percentage of useful ETs in NetIO with synthetic noise, 12,000-instruction total history length, and varied history item granularity                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.5 | Evaluation of ColorSafe for debugging. Number of code points reported by ColorSafe using deployment mode, debugging mode, and debugging mode with invariant post-processing                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.1 | Aviso's runtime overheads. These overheads are relative to baseline execution when collecting events only and when collecting events and avoiding failures                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.2 | Aviso's dynamic behavior. Columns 2 and 3 show the total number of sharing events and the number of sharing events discarded due to online pruning. Columns 4 and 5 show the total number and number discarded of synchronization and signaling events. Column 5 shows the number of times an event in an available constraint executes, requiring a check to see if the event activates the constraint. Column 6 shows the number of times a check actually leads to a constraint's instantiation. Column 7 shows the number of times an event is delayed by a constraint |

| 8.1 | Categories of prior work discussed in this chapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### **ACKNOWLEDGMENTS**

This dissertation is the culmination of years of work that I have done under the guidance of incredible mentors who have led me to where I am from my naive beginnings. First and especially, I need to thank my advisor, Luis Ceze. I lucked out working with Luis. His effervescent attitude and creativity have shaped who I am as a researcher and a person. Luis helped to guide my intuitions and taught me how to really look at, and understand things. In advising me, Luis has put up with a lot from me, which probably required more patience than I realize. He has also fueled my wanderlust, by sending me around the world to preach about the research we've done together. Thanks for showing me the ropes, it really means a lot.

I have also appreciated Mark Oskin's irreverence and cynicism – well-applied, these yield the freshest insights. His mentorship has helped me calibrate my personal and professional worldview. Dan Grossman's vulcan lucidity and ability to focus on the essential has helped me to occasionally think before I speak — this ability may come in handy. Susan Eggers's advice and experience wrangling undergraduate students has been instructive and I value having taught alongside her. I appreciate Mike Ernst's candor, clarity, and willingness to help me improve my research and exposition.

Looking further back, I am reminded of how I ended up doing research to begin with. Soha Hassoun at Tufts University led me to my first steps down this path. Without her influence, I am unsure I would even know that the world of research exists. It was good times staring down boolean constraint systems for hours in the lab in Halligan Hall. Sam Guyer, too, helped to guide me toward research while I was at Tufts. I never did get around to finishing that object inlining code, but working together was enriching, nonetheless.

Looking yet further back, to past mentors from before my time at Tufts is difficult because it feels like eons have passed. Several stand out. Ed Dignum gave me self-confidence and his mentoring trained me to be a speaker. Anthony Cassale saw promise in my interest in computers early on and I can't thank him enough for challenging me to write Pac-Man in Pascal. Todd Koza showed me Linux for the first time and, probably without knowing it, changed my life.

It is a true privilege to have had such guidance from such incredible mentors.

Aside from my mentors, the student members of SaMPA have also been professionally and socially enriching during my formative academic years and I must thank them all for ideas, feedback, and inspiration. Especially: To Joe Devietti for being one of the most balanced people I know. And of course, for finishing your PhD first; To Adrian Sampson for giving me something to aspire to when I'm making a talk and for lots of good times at conferences. To Jacob Nelson for your empathy, ability to make the cluster work, and often surprising knowledge of very specific subjects. To Nick Hunt, for help writing under fire and for having the self-awareness to follow your ambitions. To Ben Wood for your spirit of adventure and awesome connectionist sense of humor, immortalized multiple times in the proceedings of PoCSci. To Tom Bergan for your candid and constructive way of looking at things, and your good sense as a real engineer. To Hadi Esmaeilzadeh, for commiseration over job search gripes when we were both figuring out where we were headed.

In addition to my labmates, I must thank the cohort of others with whom I have worked during my time as a PhD student. It was a pleasure to collaborate on research with Hans Boehm, Karin Strauss, Shaz Qadeer, Laura Effinger-Dean, Emily Fortuna, and Todd Schiller.

Apart from my colleagues, the people in my life deserve gratitude that would fill far more than the space on this page. Especially: To Nicki for companionship, tolerance, support, encouragement and sense of belonging. Your perspective on life helps me to keep in mind what is important and to not take life too seriously. You make me a happy person. To Tony Fader, for being a great friend, unpretentiously intellectual, and a source of humor and inspiration. To Matt D'Arcangelis for being a great friend, for temperingly looking outward, helping me not to forget who I am. To Morgan, Franzi, Greg, Nell, Cliff, Todd, Pete and

everyone else for being wonderful friends over the years. For games nights, barbecues, happy hours, post-TGIF fun, etc., that happily perforated the work-time of grad school. To the Racer Sessions and the people that make it special, for keeping me creative and amongst others who are even more creative. I also must nod to my recent past lives because they put me where I am now: Julia Verplank, the Quigleys (Katie and Rich), Bop Street Records, and The Foghorns. Life outside of grad school facilitated life inside grad school and all of these things are valuable to me.

Finally and especially, I am grateful beyond anything I could write for my family's unflagging support for my entire life and throughout my education. My parents influence and encouragement to seek education is what led me to my ambitions. Summers in Fonda, NY gave me the work ethic and perspective I needed for a PhD. You were always there when I needed you whether I realized it at the time or not. To my siblings: it's been inspiring that we're all so individual. It's often a relief to hang out with you guys.

And to all the people in my life that I've forgotten, I appreciate you too.

## **DEDICATION**

To my parents and siblings for making me who I am

—and—

To the people in my life for being who you are.

Der Mensch kann tun was er will; er kann aber nicht wollen was er will.

— Arthur Schopenhauer

# Chapter 1

#### THE CONCURRENT SOFTWARE RELIABILITY PROBLEM

The rate of improvement in performance of sequential computation resulting from device scaling has begun to lag behind the scaling trend projected by Moore's Law [95]. A recent study [42] attributes this change to the failure of device physics to follow the scaling projections made by Dennard [35]. As a result, system designers have turned to parallelism as the primary means to increase the performance of programs. Most modern, commercially available computer systems have multiple processor cores. These parallel computing resources may be within a multicore chip, within a system across several chips, or even spanning several different machines, as in a warehouse-scale or datacenter computer. To take advantage of parallel computer systems, programmers must write programs that orchestrate computations that can run in parallel. Exposing parallel work to parallel computing resources ensures resources remain utilized, resulting in efficient, high-performance computation. In addition to the need for parallel software to utilize parallel computation resources, there is a similar need by many applications for *concurrency*. Concurrent computations are logically simultaneous computations that may share resources. For example, cloud and server applications must coordinate communication and resource sharing by simultaneous client requests. Regardless of whether concurrent computations are executed in parallel or multiplexed on a single computing resource, sharing and communication require concurrency control.

A goal in writing software – sequential, concurrent, and parallel – is that it should be written correctly, (without programming errors or "bugs") and must execute reliably (without "failing"). Software has grown essential to the function of the world, controlling infrastructure, facilitating communication, disseminating information, and acting as a platform for the global economy. When software has bugs that cause it to fail, these essential roles

that it plays are interrupted. Sometimes, such interruptions have grave consequences [10] or cost stakeholders millions of dollars [11]. NIST estimates the cost of preventable software bugs to be a non-negligible fraction of the GDP of the US [99].

Making software correct and reliable is difficult. Writing, testing, and debugging software is a challenge that has been studied for years in academia and industry. A large fraction of this effort has been devoted to making sequential software correct and reliable. A key barrier to reliability is that software often has a vast space of possible states, many of which are dependent on the computation's input or the environment in which the software is executing. The state space that emerges, given a program's structure, possible inputs, and possible execution environments is highly complex. A programmer must consider all the possible program states and reason that each behaves according to the specification of the software. Ensuring that this is the case is usually done through some combination of careful code-writing, judiciously applied testing, trial and error debugging, and various development tools. The complexity of the state space is what makes it challenging to create correct, reliable sequential software.

Concurrency and parallelism exacerbate the difficulty of making correct, reliable software. As in sequential software, in concurrent and parallel software, the state space is in part defined by the program's structure, the possible inputs, and the environment in which the program may execute. With concurrency and parallelism, however, the space is fundamentally more complex. The often extremely large number of possible interactions between concurrently executing computations increases the size of the space. The manner in which computations are carried out in parallel—scheduling, resource allocation, and parallelization strategy—also impact the size of the state space of the program.

The fundamental increase in complexity for concurrent and parallel software as compared to sequential software presents several challenges to programmers. It is more difficult to write programs that correctly execute computations in parallel. It is a challenge to correctly coordinate the sharing of resources by concurrent computations. It is difficult to find, understand, and fix errors related to parallelism and concurrency. The increased complexity of the state space of concurrent and parallel programs makes testing substantially more complicated. The difficulty in testing means that some bugs will not be found and may

surface only in production systems, causing those systems to fail.

The work in this dissertation focuses on the correctness and reliability of concurrent and parallel programs. This work develops novel techniques that simplify the process of debugging concurrent programs and that make software execute reliably in production *despite* latent bugs in deployed code. These techniques are realized through the use of novel computer architecture and system support implemented in both the hardware and software layers of a computer system. A high-level statement of the thesis of this work follows:

**Thesis Statement:** Novel system and architecture support addresses the complexity of concurrent and parallel software by making it easier to debug and by making it execute without failing, despite bugs in code.

The remainder of this chapter is devoted to providing context for the work in this dissertation. First, we describe shared-memory multi-threaded programming, the model of computation around which we conducted this work. Second, we describe the types of bugs and failures addressed in this work. Third, we discuss the main challenges addressed in this work. Fourth, we describe each of the contributions of this dissertation in brief, foreshadowing later chapters that describe them in detail.

#### 1.1 Concurrency and Parallelism in Shared-memory Multi-threaded Programs

While there are many different models for writing concurrent and parallel software (e.g., [20, 7, 6, 8, 2]), one of the most common is shared-memory multi-threaded programming. The work in this dissertation focuses on shared-memory multi-threaded programs. Unlike sequential programs that have a single thread of control, multi-threaded software has multiple threads of control. Each thread executes its own instructions in some sequence. Threads interact by sharing data and synchronizing. To share data, threads perform read and write operations that load values from and store values to locations in a shared address space. Operations performed by different threads are unordered by default: there are no implicit constraints on the order of execution of different threads' operations. Using synchronization [57, 72, 5], a programmer can impose an order on two operations in different threads.

Figure 1.1: An illustration of a shared memory multi-threaded program execution. The threads execute memory accesses (squares) that can read and write values to a shared memory space. Each thread executes its operations sequentially, but different threads' operations are independent and unordered by default. Threads can use synchronization operations (circles) to impose an ordering on operations in different threads that would otherwise be unordered.

When two operations are ordered in an execution by executing in the same thread or by synchronization, the first is said to have *happened before* the other. The ordering imposed is referred to as the "happens-before order" [71] for that execution and it is an irreflexive partial order on the events in the execution. Figure 1.1 illustrates several aspects of a shared-memory multi-threaded program's execution.

As a program executes, threads observe an execution schedule of their and other threads' memory and synchronization operations that corresponds to the execution's happens-before order. The execution schedule shows the order of operations in an execution and determines which read operations in the program read values written by which write operations. There are two important factors that determine the observed execution schedule for a particular execution.

• Synchronization Order: The order in which synchronization operations are executed may vary. The function of synchronization operations is to determine the order of other operations in a program's execution. Synchronization operations themselves, however, do not have a fixed a priori order at the program's start. Differences in the timing of operations in different executions can alter the order in which threads reach

synchronization points. The variation in the order in which threads arrive at synchronization points can in turn vary the order of other operations in the execution. These variations imply that different executions may have different execution schedules.

• Data Races: Happens-before is a partial order over the operations in an execution, meaning some operations are not ordered before or after one another. These operations are concurrent. A pair of concurrent operations conflict if they both access the same piece of shared state (i.e., the same variable) and at least one of the operations modifies the state (i.e., performs a write operation). The concurrency of non-conflicting, concurrent operations in an execution schedule is inconsequential: such operations do not access similar state or synchronize, so they cannot have any effect on one another. In contrast, the execution of two concurrent, conflicting operations constitutes a datarace. The execution semantics of racy operations is tricky: the accesses conflict, so their execution order may affect their outcome, but the accesses are concurrent, so their order – and thus their outcome – is unclear. The outcome of a data-race can vary nondeterministically from one execution to the next. Data-races are a major challenge. Section 1.2.1 describes the mechanics of data-races and the problems they present in more detail.

The execution schedule of a program can vary from one execution to the next because of data-races and variation in the order of synchronization. That variation implies that there are many, different, possible, valid execution schedules for a program. A given execution may follow any of those schedules – the schedule that an execution follows is nondeterministic from one execution to the next. Nondeterminism is an important property of shared-memory multi-threaded programs because different execution schedules can lead to different results, even with the same input.

Figure 1.2 illustrates how operations can execute in a different order from one execution to the next, assuming an arbitrary memory model to resolve the order of racy operations. Figure 1.2(a) shows the pseudocode of a simple program with three threads, T1, T2, and T3. T1 is assigning a shared pointer, p, to point to a new object and then releasing a lock.

Figure 1.2: Different executions of a shared-memory multi-threaded program

T2 acquires the lock, assigns a new value to a shared variable, q, and then releases the lock. T3 reads the value of q into a local variable, t, and then uses p by dereferencing it. p is assumed to be uninitialized at the start of the execution. q is assumed to be 0 at the start of the execution. Figure 1.2(b) shows one execution, leading to one result state. Figure 1.2(c) shows a different execution leading to a different result state.

Figure 1.2(a-c) illustrates that variation in the execution schedule can vary the result of a computation. Figure 1.2(d) shows how variation in the execution schedule can even determine whether a computation fails or succeeds. The operations in **C** and **D** are not ordered with the operations in **A**. When **C** and **D** occur in the execution schedule without observing the result of the code in **A**, the pointer dereference in **D** dereferences **p** before it has been initialized by the assignment in **A**. Assuming, as many languages do [4, 24, 88], that dereferencing an uninitialized pointer is illegal, such a schedule leads to a failure. The synchronization that the programmer wrote is buggy and permits the execution schedule shown in part (d) that leads to a failure.

In most programs, most execution schedules behave as the programmer intended. How-

ever, as Figure 1.2(d) shows, when the programmer has written buggy code, that code may permit schedules that cause the program to do something that it was not intended to do (like crash). The bug in Figure 1.2(a) is a concurrency bug. Concurrency bugs are errors in code that can lead to schedule-dependent failures. A schedule-dependent failure is any unintended program behavior that is the result of particular orderings of operations in different threads. These failures are called "schedule-dependent" because their occurrence depends on the occurrence of execution schedules that exhibit those particular orderings. Concurrency bugs and the schedule-dependent failures they cause are two fundamental barriers to correctness and reliability in concurrent programs.

#### 1.2 Concurrency Bugs and Schedule-Dependent Failures

In shared-memory multi-threaded programs, concurrency bugs are errors in code that coordinates inter-thread interactions, like ordering operations and sharing data. Concurrency

bugs show up as incorrectly used synchronization operations and patterns of accesses to

memory shared by multiple threads that lead to unintended behavior. There are many

types of concurrency bugs that lead to schedule-dependent failures [79]. The next sections

discuss some of the most common types, including data-races, atomicity violations, ordering

violations, as well as some important variations on these classes of errors.

#### 1.2.1 Data-Races

No discussion of concurrency errors would be complete without a discussion of data-races. A data-race occurs when two threads each perform an access to the same memory location, at least one of the threads' accesses is a write, and the accesses are not ordered by synchronization (*i.e.*, happens-before). Many popular programming language definitions ascribe executions of programs with data-races undefined [4, 24, 5] or unintuitive [88] semantics. The intent of these semantics is to permit aggressive instruction reordering optimizations in compilers and architecture, without excessive restriction from the language. Despite weak or overly complex language-level semantics, most computer systems execute programs with data-races and the ordering semantics of racy operations is determined by the architecture

level memory model [109, 120, 9, 52]. An architecture's memory model determines, for each point in an execution, the value that a read (racy or otherwise) of shared state may observe.

Data-races lead to variation in the execution schedule. All data-races are not necessarily schedule-dependent failures, but many are and the behavior of data-races is hard to reason about. Some in the research community take the strong position on data-races that, because language-level semantics and architecture-level memory models make reasoning about dataraces so difficult, any code that permits a data-race is buggy and no data-race is benign [23]. Why are data-races so hard to reason about? The root of the difficulty presented by data-races is that programmers typically reason about their programs assuming a memory model under which all executions are Sequentially Consistent or SC [71]. In an SC execution the same order of operations is observed by all threads and threads' operations execute in their original program order. Unfortunately, most architecture memory models do not guarantee SC in all circumstances. Instead, they provide some form of relaxed consistency. Relaxed consistency allows systems to use aggressive optimizations that can reorder a thread's operations and cause threads to observe different execution orders. In executions with no data-races, these reorderings cannot have any effect on the behavior of the program. When a program has data-races, however, reorderings involving racy operations can change the program's behavior from one execution to the next. Reordering of racy operations can also result in unintuitive behavior that violates SC and causes a program's execution to apparently defy causality. <sup>1</sup>

The work in this dissertation does not explicitly address SC violations that stem from dataraces — other work by this author [84, 38] and plentiful work by other authors (e.g., [45, 141, 89, 90]) addresses this dimension of data-races. Instead, this dissertation treats data-races as sub-sequences of the execution schedule that can vary from one execution to the next, sometimes leading to failure behavior. These variations may lead to violations of SC, or may be a source of nondeterminism only. In either case, if the reorderings lead to behavior that violates the specification of the program, then the code involved in the data-race constitutes

<sup>&</sup>lt;sup>1</sup>A detailed discussion of memory models, reordering, and consistency is outside the scope of this dissertation. A gentle introduction to the subject can be found in this tutorial [12] and in this primer [124].

a concurrency bug. Other types of concurrency bugs discussed in this section may involve operations that race.

#### 1.2.2 Atomicity Violations

Atomicity violations are another common type of concurrency error. Critical to understanding atomicity violations are the concepts of *Atomicity* and *Isolation*.

- Atomicity is a property of a sequence of program operations. A sequence of operations are atomic only if all of their results become observable by other threads simultaneously. Other threads may observe none of the results of the atomic instructions or all of the result of the atomic instructions, but never the result of some and not of others.

- Isolation is a property of a sequence of program operations. A sequence of operations are isolated if the result of their execution concurrently with code in other threads is the same as the result of their execution in the absence of other threads. Other threads may not observably access the same state as an isolated computation while it is executing, nor may the isolated computation observably access the same state as the other threads' computations.

Programmers often intend for a sequence of operations to be atomic and isolated. The atomicity and isolation of a region of code can be ensured with proper use of synchronization. An execution of a program with a concurrency bug that omits or incorrectly uses synchronization to enforce atomicity may fail due to an atomicity violation. An atomicity violation is a type of failure that can afflict a region of code intended to be atomic and isolated. If such a region accesses some shared memory locations and its execution is interleaved by instructions in another thread that access the same locations, the interleaving may violate the atomicity of the region of code.

Figure 1.3 shows how an interleaving permitted by a concurrency bug can lead to an atomicity violation. The code in Thread 1 deletes and subsequently reallocates the data

Figure 1.3: Code with a concurrency bug that can lead to an atomicity violation failure.

pointed to by p. Thread 1's code should execute atomically. When Thread 2's code *interleaves* between Thread 1's manipulations of p, Thread 2 dereferences a deleted pointer, leading to a crash. The code in Thread 1 that should have been atomic is implemented incorrectly. A single locked critical region should contain the delete and the reallocation, not two separate regions.

Some interleavings with regions of code intended to be atomic lead to atomicity violations. The interleavings that lead to atomicity violations are unserializable. Serializability [102] is a property of a concurrent execution. A concurrent execution is serializable if its result is the same as some sequential execution of the regions of code in the execution that were intended to be atomic. If a region of code was intended to be atomic and the outcome of that region is changed simply because some other code interleaved between the operations in that region, then the interleaved execution was unserializable. Put another way, when an interleaving can change an execution's behavior, it is unserializable. Atomicity violations stem from unserializable interleavings of regions of code intended to be atomic. Prior work

has shown [44, 48, 80, 136] that if an execution is serializable (with respect to some specified atomic regions), then there were no atomicity violations.

The connection between atomicity violations and serializability makes serializability a useful property. Serializability analysis facilitates reasoning about the difference between atomicity constraints that were implemented by a programmer (e.g., using locks), and those that were specified in the program's design (e.g., in a specification). However, the problem of atomicity violations runs deeper than simply checking the serializability of specified atomic regions: Often there is no correct specification of the regions of code in a program that were intended to be atomic. The absence of atomicity specifications has two effects: (1) Programmers often incorrectly reason about which code should be atomic and isolated. They use synchronization incorrectly, and write broken code that suffers atomicity violations. (2) Detecting atomicity violations requires inferring atomic code regions, which is difficult.

Bugs leading to atomicity violations are very common. The work in this dissertation develops several techniques for debugging such bugs and avoiding atomicity violations.

#### 1.2.3 Ordering Violations

Ordering violations are another common class of concurrent programming mistakes [79]. Ordering errors consist of a pair of operations that should execute in a particular order, but for which synchronization constraints are absent, permitting them to execute out of order. Some ordering violations involve accesses that constitute a data-race. Other ordering violations involve only synchronized accesses, although in these cases, the synchronization does not enforce the correct order of the operations, only that there is no data-race. To prevent failures due to ordering violations, programmers must use synchronization to ensure that the correct event order occurs in all executions. The bug in Figure 1.2(a) leads to an ordering violation that involves racy accesses to p in A and D.

#### 1.2.4 Multi-variable Concurrency Errors

There are several variants of each of the types of concurrency errors discussed so far. One important axis along which the errors can vary is the amount of data referred to by oper-

ations involved in the error. Prior work has primarily characterized errors as being either single-variable or multi-variable errors [14, 78, 80, 55, 83, 81, 86]. The operations making up single-variable errors all access the same memory location; the operations making up multi-variable errors may access several different memory locations.

- (a) A program with a concurrency bug involving multiple variables. o.str and o.len represent related properties of a string. When one is update, the other should also be updated and the updates should be atomic. Thread 1 is executing buggy code that updates both properties, without atomicity. Thread 2 is also updating both properties

- (b) An execution schedule with an atomicity violation. Thread 2's update of the variables interleaves between Thread 1's. At the end of both threads, the variables' values are not consistent with one another.

Figure 1.4: A concurrency bug involving multiple related variables that can lead to an atomicity violation.

Data-races are inherently single-variable errors because a data-race is defined as a pair of accesses to the same memory location (although some prior work has expanded the notion of a data-race to consider races at a coarser data-granularity [129]). Atomicity violations and ordering violations can involve either a single variable or multiple variables. Multi-variable variants of atomicity and ordering errors are more complex than their single-variable counterparts. The complexity arises from the need to consider not just interactions between threads involving a single piece of state, but rather, arbitrary subsets of the program's state (i.e., groups of variables).

Figure 1.4(a) illustrates a multi-variable concurrency bug. The code in the figure has

two threads. Both threads are attempting to update two related properties of an object, o that represents a string's contents (o.str) and its length (o.len). The properties are semantically related to one another. If one property is updated, the other must be updated to maintain the consistency of their relationship. Furthermore, the updates must happen atomically. Thread 2 correctly uses synchronization to make its updates the variables atomic. However, Thread 1 uses synchronization incorrectly, failing to ensure the atomicity of its updates. Figure 1.4(b) shows an execution of this program in which Thread 2's code violates the atomicity of Thread 1's code. When that happens, the result of the two updates inconsistent: o.str is the empty string ("") and o.len is 1.

#### 1.2.5 Other Concurrency Errors

The list of errors in this section is not comprehensive. Instead, this list has focused on errors addressed by the work in this dissertation. There are other types of concurrency errors, such as deadlocks [31] and livelocks, which prevent executions from making any progress, as well as errors involving thread interactions via shared resources other than shared memory [69]. The work in this dissertation is applicable to some deadlocks and livelocks, but does not address errors that involve accesses to resources other than shared memory.

#### 1.3 Challenges Addressed by this work

There are two goals to the work in this dissertation: (1) to simplify the process of finding, understanding, and fixing concurrency bugs; and (2) to develop techniques that automatically avoid schedules that lead to schedule-dependent failures, even in programs with concurrency bugs that permit those schedules. Concurrency debugging and schedule-dependent failure avoidance are essential challenges presented by concurrent and parallel software.

#### 1.3.1 Debugging Concurrency Bugs

The goal of programmers is to find the bugs in their programs and to fix those bugs. Programmers test their programs and use bug-finding tools to uncover indicators of bugs in their code, like bug reports and failed test cases. Starting from those indicators, program-

mers must then understand the bug and determine what code changes are necessary to fix it. There are several reasons why debugging concurrency bugs is especially difficult.

- 1. Complexity of execution schedule space. The execution schedule can vary from one run to the next nondeterministically. The space of possible execution schedules that a program may exhibit is very large. It is often not obvious from code alone which execution schedules may lead to failure, or even which schedules are possible in the first place.