**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

**UMI**

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

| <br> | <br> |  |

|------|------|--|

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      | ·    |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

# On the Use and Performance of Communication Primitives in Software Controlled Cache-coherent Cluster Architectures

by

## Xiaohan Qin

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

University of Washington

1997

| Approved by       | Voar-u            | Sun            |                   |               |  |

|-------------------|-------------------|----------------|-------------------|---------------|--|

|                   | (Chairperson of S | Supervisory Co | $\mathbf{mmitte}$ | ee)           |  |

|                   |                   |                |                   |               |  |

|                   |                   |                |                   |               |  |

| <del></del>       |                   |                |                   |               |  |

|                   |                   |                |                   |               |  |

| Program Authorize | ed                | <b>C</b> ,     | æ                 | <b>-</b> .    |  |

| to Offer Degree   | Compular          | Science        | <del>_</del> _    | En gi reering |  |

| Data              | 12/12/97          |                |                   |               |  |

UMI Number: 9819293

Copyright 1997 by Qin, Xiaohan

All rights reserved.

UMI Microform 9819293 Copyright 1998, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

UMI 300 North Zeeb Road Ann Arbor, MI 48103 © Copyright 1997

Xiaohan Qin

In presenting this dissertation in partial fulfillment of the requirements for the Doctoral degree at the University of Washington, I agree that the Library shall make its copies freely available for inspection. I further agree that extensive copying of this dissertation is allowable only for scholarly purposes, consistent with "fair use" as prescribed in the U.S. Copyright Law. Requests for copying or reproduction of this dissertation may be referred to University Microfilms, 1490 Eisenhower Place. P.O. Box 975, Ann Arbor, MI 48106, to whom the author has granted "the right to reproduce and sell (a) copies of the manuscript in microform and/or (b) printed copies of the manuscript made from microform."

#### University of Washington

#### Abstract

On the Use and Performance of Communication Primitives in Software Controlled Cache-coherent Cluster Architectures

by Xiaohan Qin

Chairperson of Supervisory Committee: Professor Jean-Loup Baer

Computer Science and Engineering

Two recent trends are affecting the design of medium-scale shared-memory multiprocessors. The first is the use of nodes which themselves consist of clusters of processors. Clusters, already available as commodity parts, not only make powerful nodes, they also let the system scale up gracefully. The second trend is the use of programmable protocol processors and software for maintaining cache coherence to shorten the hardware design cycle and to provide flexibility and extensibility.

One problem arising from software cache coherence is that remote memory accesses suffer a longer latency than with a pure hardware scheme. Another issue raised by software schemes in cluster environments is that of contention on the protocol processor due to the high service demand for this device.

Our solution to the first problem offers users or compiler writers a set of explicit communication primitives to provide hints for moving data properly and promptly. The communication primitives, running on protocol processors, introduce a flavor of message-passing and permit protocol optimization. To the second issue, we investigate three architectural choices that strive to achieve resource balance: (1) selecting an appropriate cluster size to control resource sharing, (2) adding a remote cache (per

node) to keep remote data in clusters, and (3) adding a forwarding logic to reduce the load on the protocol processor and to speed up the processing of simple messages.

This dissertation studies how the overhead of a software scheme and its contention on the protocol processor can be reduced by various combinations of the design options and how the software overhead can be further hidden by the communication primitives. In the absence of communication primitives, we employ an MVA-based analytical model to estimate the protocol processor's contention and overall performance for a fast turn-round. When communication primitives are present, we employ simulation method. We find that the software implementation supplemented with remote cache and forwarding logic can deliver a performance competitive with the rigid and pure hardware scheme. With the judicious use of communication primitives, the enhanced software scheme can improve performance beyond the limit of the hardware implementation. In addition, the software cache coherence is more flexible, scalable and easier to optimize.

## TABLE OF CONTENTS

| List of | Figures                                                  | iii |

|---------|----------------------------------------------------------|-----|

| List of | Tables                                                   | vii |

| Chapte  | er 1: Introduction                                       | 1   |

| 1.1     | Motivations                                              | 1   |

| 1.2     | Contributions                                            | 4   |

| 1.3     | Organization of the Thesis                               | 6   |

| Chapte  | er 2: Architectural Framework                            | 7   |

| 2.1     | Baseline Architecture and Components                     | 7   |

| 2.2     | Cache Coherence Protocols                                | 14  |

| 2.3     | Cache Coherence and Split Transaction Devices            | 18  |

| 2.4     | Software Implementation of the Directory Protocol        | 22  |

| 2.5     | Summary                                                  | 25  |

| Chapte  | er 3: Communication Primitives in Uni-processor Node Ar- |     |

|         | chitectures                                              | 27  |

| 3.1     | Explicit Communication Primitives                        | 28  |

| 3.2     | Implementation Issues                                    | 30  |

| 3.3     | Experimental Methodology                                 | 33  |

| 3.4     | Performance Results                                      | 38  |

| 3.5     | Related Work                                             | 51  |

| 3.6                                | Summary                                                                        | 53                                  |

|------------------------------------|--------------------------------------------------------------------------------|-------------------------------------|

| Chapte                             | er 4: Modeling Contention on Shared Resources                                  | 55                                  |

| 4.1                                | Design Options                                                                 | 56                                  |

| 4.2                                | Analytical Model                                                               | 59                                  |

| 4.3                                | Application parameters                                                         | 69                                  |

| 4.4                                | Exercising the Model: Performance Evaluation                                   | 74                                  |

| 4.5                                | Validation                                                                     | 82                                  |

| 4.6                                | Related Work                                                                   | 83                                  |

| 4.7                                | Summary                                                                        | 86                                  |

|                                    |                                                                                |                                     |

| Chapte                             | er 5: Communication primitives in cluster architectures                        | 89                                  |

| Chapte<br>5.1                      | Er 5: Communication primitives in cluster architectures  Implementation Issues | <b>89</b><br>90                     |

| •                                  |                                                                                |                                     |

| 5.1                                | Implementation Issues                                                          | 90                                  |

| 5.1<br>5.2                         | Implementation Issues                                                          | 90<br>94                            |

| 5.1<br>5.2<br>5.3                  | Implementation Issues                                                          | 90<br>94<br>95                      |

| 5.1<br>5.2<br>5.3<br>5.4           | Implementation Issues                                                          | 90<br>94<br>95<br>110<br><b>112</b> |

| 5.1<br>5.2<br>5.3<br>5.4<br>Chapte | Implementation Issues                                                          | 90<br>94<br>95<br>110<br><b>112</b> |

## LIST OF FIGURES

| 2.1 | Model of the cluster architecture                                         | 0  |

|-----|---------------------------------------------------------------------------|----|

| 2.2 | Model of the communication processor                                      | 9  |

| 2.3 | Choices of memory access path                                             | 11 |

| 2.4 | Memory sub-operation ordering                                             | 19 |

| 2.5 | A deadlock-prone scenario                                                 | 20 |

| 2.6 | Coherence directory data structures                                       | 23 |

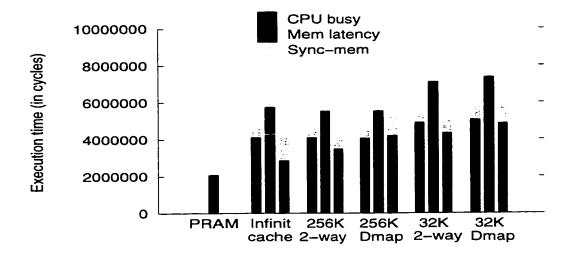

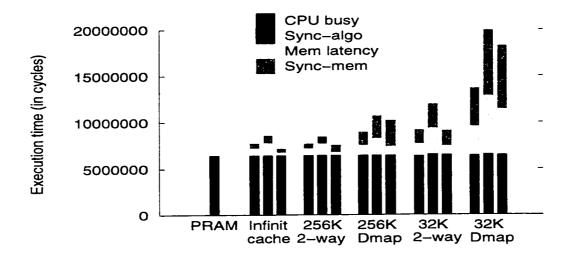

| 3.1 | Execution times for FFT. "CPU busy" is the compute processor execu-       |    |

|     | tion time. "Mem latency" is the amount of time the compute processor      |    |

|     | waits because of memory latency and cache coherence effects. "Sync-       |    |

|     | Mem" is the synchronization time, including load imbalance, due to        |    |

|     | the effect of memory latency. For each cache configuration, the three     |    |

|     | bars, from left to right, show the results of the hardware full-directory |    |

|     | implementation, the software implementation, and the optimized soft-      |    |

|     | ware implementation, respectively.                                        | 40 |

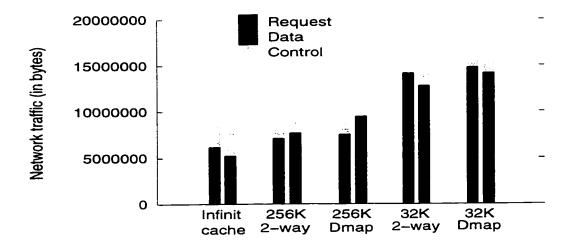

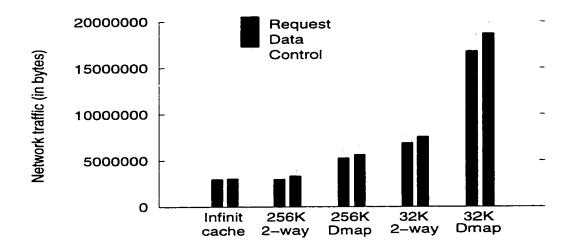

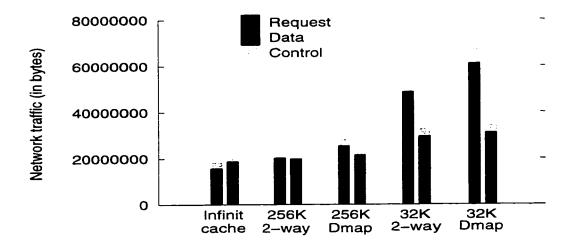

| 3.2 | Network traffic for FFT. "Request" "Data", and "Control" are the          |    |

|     | network traffic for sending cache miss requests or communication prim-    |    |

|     | itives, data, and control messages (e.g., invalidation and acknowledg-    |    |

|     | ment), respectively. The left and right bars show the network traffic     |    |

|     | for unoptimized and optimized software implementations, respectively.     |    |

|     | Network traffic for the hardware implementation is omitted since it is    |    |

|     | equivalent to that of the software implementation.                        | 44 |

|     |                                                                           |    |

| 3.3 | Execution times for LU. For a detailed explanation of the legend, refer   |       |

|-----|---------------------------------------------------------------------------|-------|

|     | to the caption of Figure 3.1. In addition, "Sync-algo" is the synchro-    |       |

|     | nization time due to load imbalance intrinsic to the algorithm.           | 45    |

| 3.4 | Network traffic for LU. For a detailed explanation of the legend, refer   |       |

|     | to the caption of Figure 3.2.                                             | 47    |

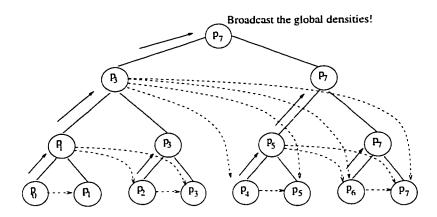

| 3.5 | Communication patterns for computing the global densities and prefix      |       |

|     | sums of the local histograms. Each processor initially has local his-     |       |

|     | tograms and local densities in its cache. The solid arrows indicate the   |       |

|     | data transfer needed for both global densities and prefix sums. The       |       |

|     | dashed curves are for prefix sums only. The label in each node is the     |       |

|     | processor that computes the intermediate or final results                 | 48    |

| 3.6 | Execution times for RADIX. For a detailed explanation of the legend,      |       |

|     | refer to the caption of Figure 3.1                                        | 49    |

| 3.7 | Network traffic for RADIX. For a detailed explanation of the legend,      |       |

|     | refer to the caption of Figure 3.2                                        | 52    |

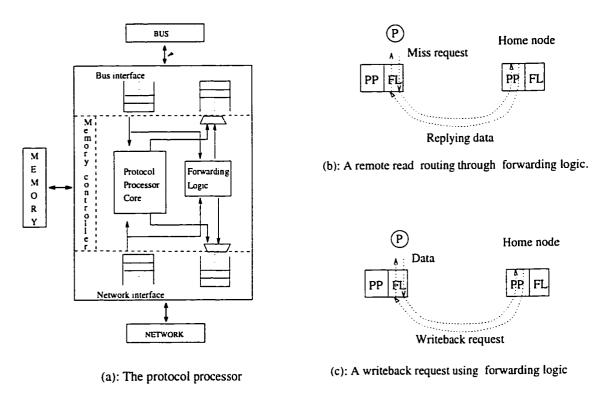

| 4.1 | The communication processor augmented with forwarding logic               | 58    |

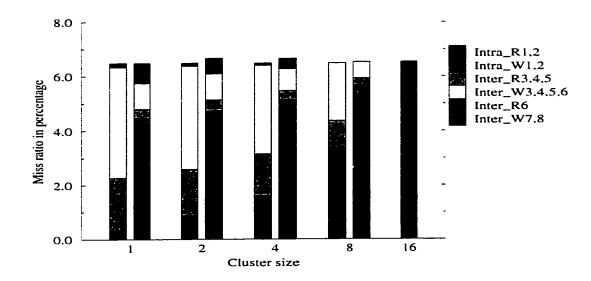

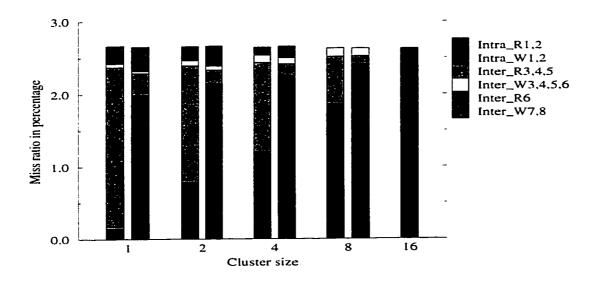

| 4.2 | The cache miss profile of RADIX. The left (right) bar of each pair cor-   |       |

|     | responds to an architecture not containing (containing) remote caches.    |       |

|     | R1,R2 and $W1,W2$ are intra-cluster misses. $R3,R4,R5$ and $W3,W4,W$      | 5, W6 |

|     | are inter-cluster misses that involve two clusters. $R6$ and $W7, W8$ are |       |

|     | misses involving three clusters. Tables 4.1 and 4.2 provide a detailed    |       |

|     | explanation of each type of miss.                                         | 71    |

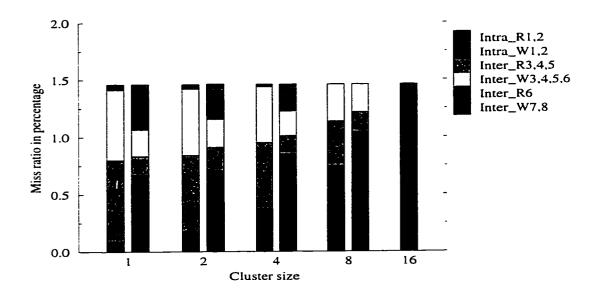

| 4.3 | The cache miss profile of FFT. For a detailed explanation of this graph,  |       |

|     | refer to the caption of Figure 4.2                                        | 72    |

| 4.4 | The cache miss profile of RAYTRACE. For a detailed explanation of         |       |

|     | this graph, refer to the caption of Figure 4.2                            | 73    |

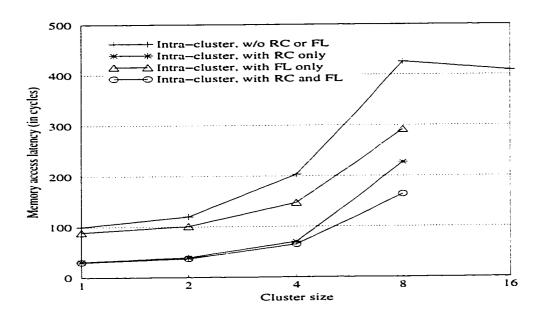

| 4.5  | The average intra-cluster cache miss latencies for RADIX. RC and FL    |     |

|------|------------------------------------------------------------------------|-----|

|      | stand for remote cache and forwarding logic respectively               | 77  |

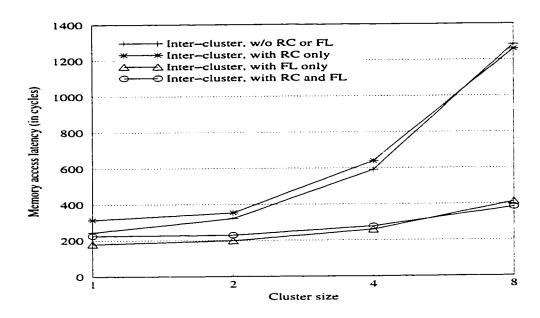

| 4.6  | The average inter-cluster cache miss latencies for RADIX. RC and FL    |     |

|      | stand for remote cache and forwarding logic respectively               | 78  |

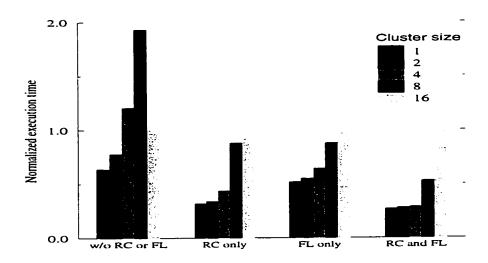

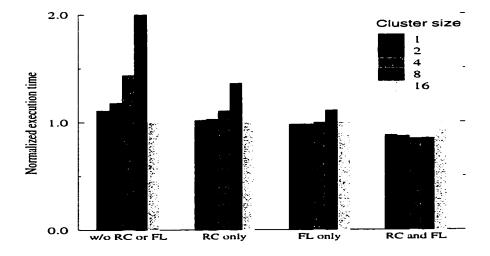

| 4.7  | Normalized execution times for RADIX                                   | 80  |

| 4.8  | Normalized execution times for FFT                                     | 80  |

| 4.9  | Normalized execution times for RAYTRACE                                | 81  |

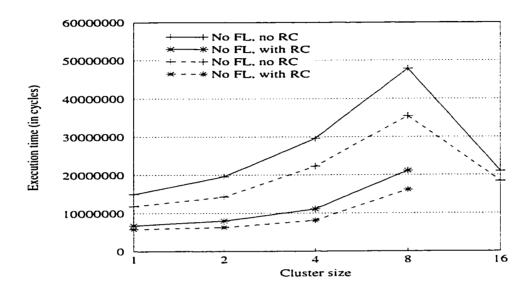

| 4.10 | Comparison of analytical and simulation results for RADIX. Solid lines |     |

|      | are simulation results. Dashed lines are the model's outputs           | 83  |

| 4.11 | Comparison of analytical and simulation results for FFT. Solid lines   |     |

|      | are simulation results. Dashed lines are the model's outputs           | 84  |

| 4.12 | Comparison of analytical and simulation results for RAYTRACE. Solid    |     |

|      | lines are simulation results. Dashed lines are the model's outputs     | 84  |

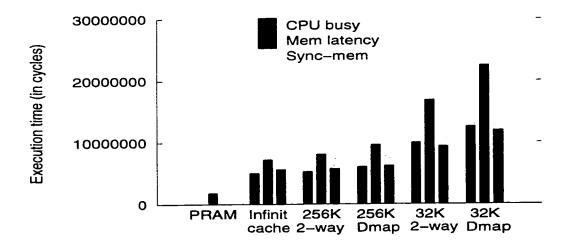

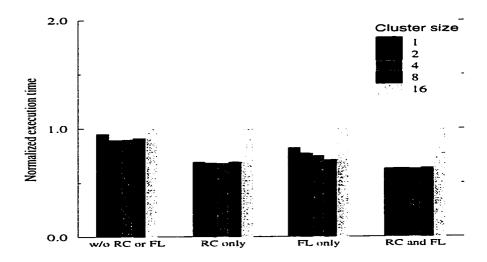

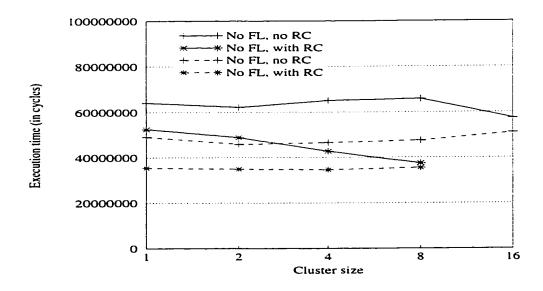

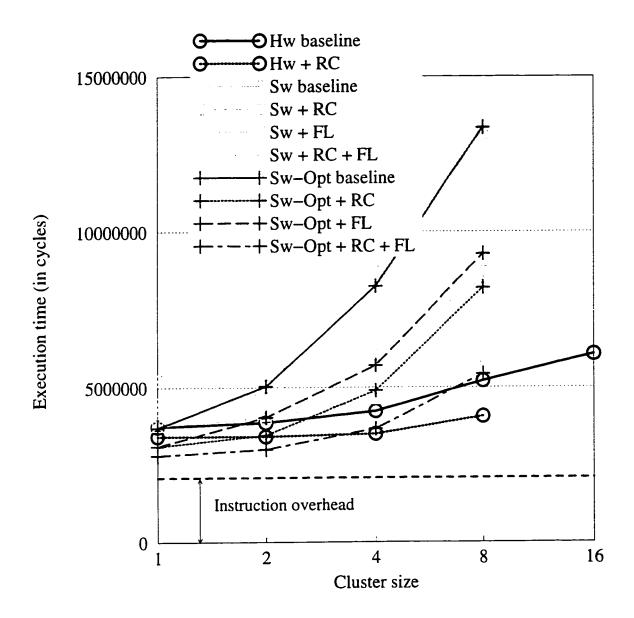

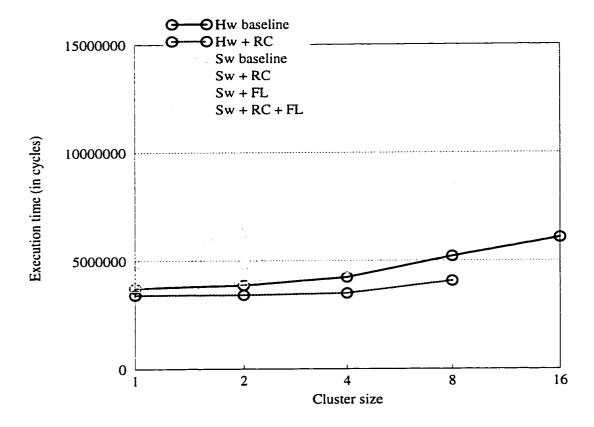

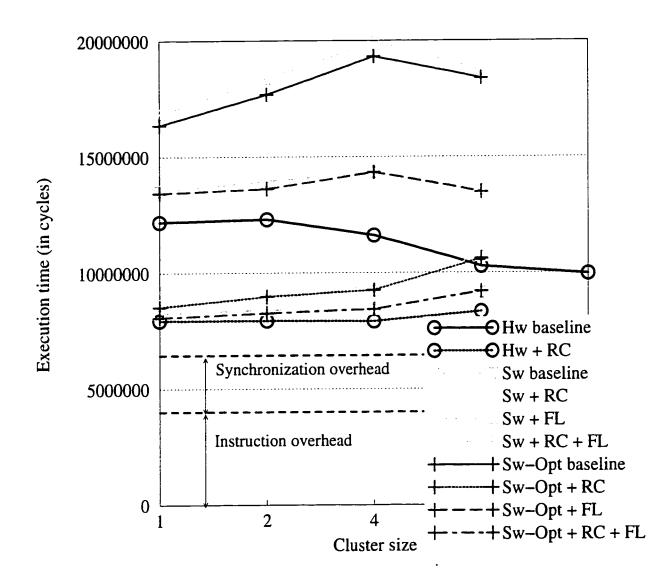

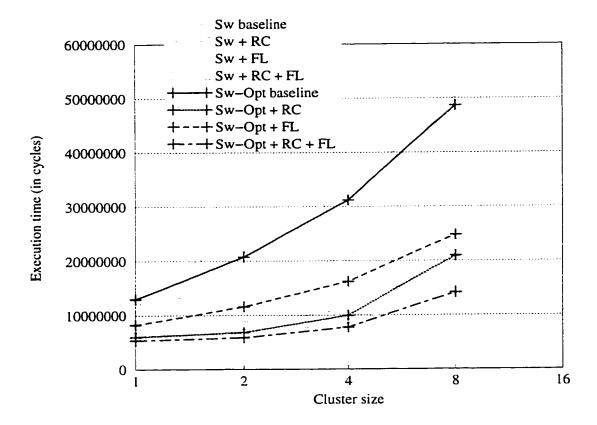

| 5.1  | Execution times for FFT                                                | 97  |

| - 0  | Execution times for FFT (hardware and software without communica-      |     |

| 5.2  | tion primitive implementations)                                        | 98  |

|      |                                                                        |     |

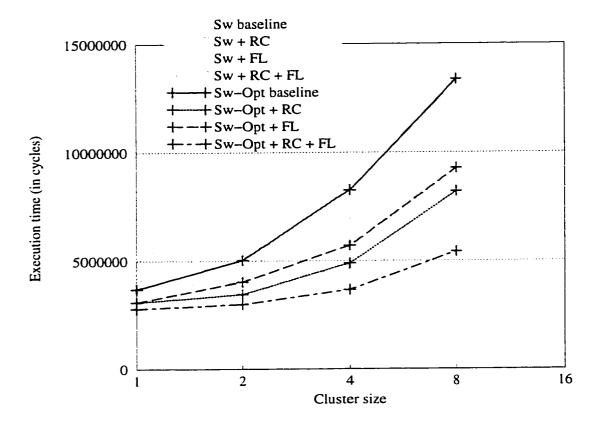

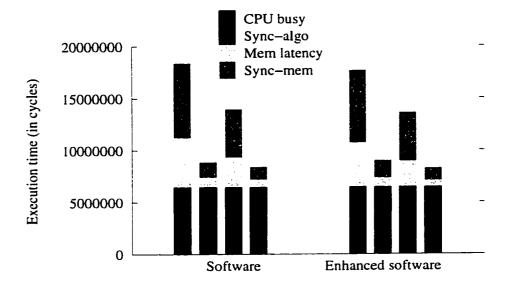

| 5.3  | Execution times for FFT (software and enhanced software implemen-      | 100 |

|      | tations).                                                              | 100 |

| 5.4  | Execution times for LU. The dashed line at the bottom represents       |     |

|      | the processor busy time and the line above it is the synchronization   |     |

|      | overhead under the PRAM model                                          | 102 |

| 5.5 | Execution times of LU: software and enhanced software implementa-           |     |

|-----|-----------------------------------------------------------------------------|-----|

|     | tion at the cluster size 2. In each group, the four bars from left to right |     |

|     | correspond to the baseline architecture, the remote cache implemen-         |     |

|     | tation, the forwarding logic implementation, and the implementation         |     |

|     | with both remote cache and forwarding logic respectively. For a de-         |     |

|     | tailed explanation of the legend, refer to the caption of Figure 3.3        | 104 |

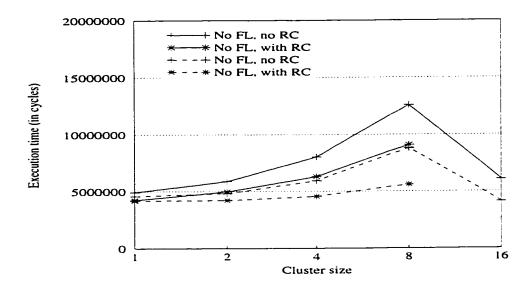

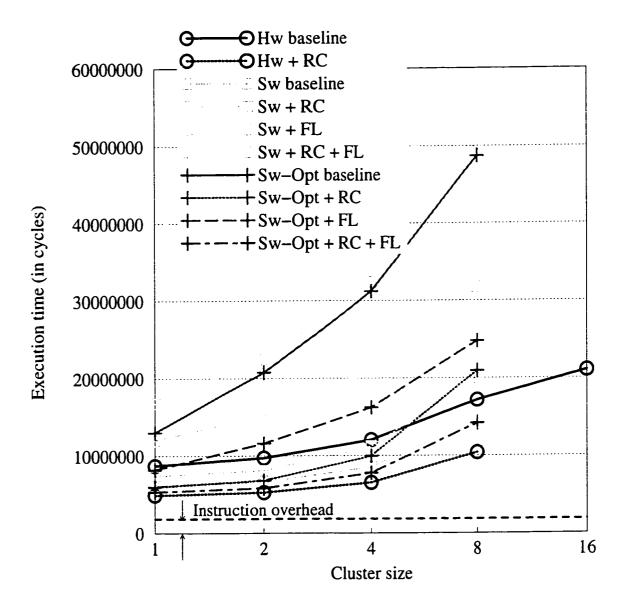

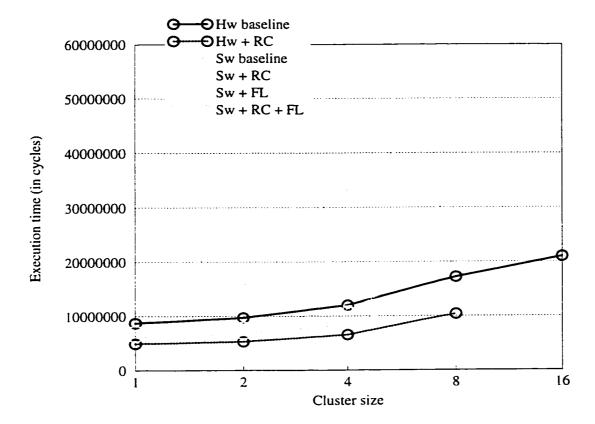

| 5.6 | Execution times for RADIX                                                   | 106 |

| 5.7 | Execution times for RADIX (hardware and software without commu-             |     |

|     | nication primitives implementations)                                        | 107 |

| 5.8 | Execution times for RADIX (software and enhanced software imple-            |     |

|     | mentations)                                                                 | 108 |

## LIST OF TABLES

| 2.1 | Network performance data for DASH and SP2                                   | 13 |

|-----|-----------------------------------------------------------------------------|----|

| 3.1 | Communication primitives. addr is the starting address of a block of        |    |

|     | data. size is its size in bytes. pid is a processor number. pids is a       |    |

|     | mask indicating a list of processors. $mode$ is either write-back $(wb)$ or |    |

|     | write-through $(wt)$                                                        | 29 |

| 3.2 | Summary of benchmark data. Numbers are given in millions                    | 35 |

| 3.3 | Principal architectural parameters of the communication processor           | 36 |

| 3.4 | Difference in timing between hardware and software implementations          |    |

|     | of a shared variable read miss. The directory for the block is in a home    |    |

|     | node different from the node requesting the data                            | 37 |

| 3.5 | Breakdown of execution times of FFT for original and optimized soft-        |    |

|     | ware implementation (infinite cache)                                        | 42 |

| 3.6 | Breakdown of RADIX's execution times for the original and optimized         |    |

|     | software implementations given a 256KB 2-way set associative cache.         | 51 |

| 4.1 | Classification of read misses.                                              | 59 |

| 4.2 | Classification of write misses.                                             | 60 |

| 4.3 | Definitions of sub-requests and resources required. Only a subset of        |    |

|     | the protocol operations are displayed. Bus transactions are counted         |    |

|     | in bus clock cycles (marked with asterisks). The other operations are       |    |

|     | counted in CPU cycles. The latencies of data transactions are for the       |    |

|     | first 8 bytes.                                                              | 63 |

|     |                                                                             |    |

| 4.4 | Service demands of read misses on shared resources. Rows of this table  |    |

|-----|-------------------------------------------------------------------------|----|

|     | show the sub-requests and the resources needed (each resource has its   |    |

|     | own column) in a given cluster for a particular type of read miss (cf.  |    |

|     | Table 4.3 for the meanings of abbreviations). For misses involving      |    |

|     | multiple clusters, the first row shows service demands for the local    |    |

|     | cluster; the second and third rows (if present) are the service demands |    |

|     | for the second and third clusters involved.                             | 64 |

| 4.5 | Service demands of write misses on shared resources. For a detailed     |    |

|     | explanation of the table, refer to the caption of Table 4.4             | 65 |

| 4.6 | Architectural parameters not included in Table 4.3                      | 69 |

| 17  | $RADIY's$ average service demands $N_s$ is the cluster size             | 75 |

#### ACKNOWLEDGMENTS

Many people have contributed to the completion of this dissertation and my Ph.D education. Their kindness and open-mindedness have made the five years of graduate student life at the University of Washington an unforgettable experience.

First and foremost, I must thank my advisor, Jean-Loup Baer, for his guidance, encouragement, support, and patience. As a Ph.D student's advisor, Jean-Loup first listens carefully to what his student has to say. It's only after that he will give his own suggestions. To do that, he put up with my insufficient English. His enthusiasm and engagement in the research made it possible for me to carry out the study. When it came to writing, his instrumental assistance allowed me to publish. It was a special privilege and a great pleasure working with him for four years. Thank you Jean-Loup!

I am grateful to Susan Eggers, Hank Levy, and John Zahorjan for serving on my committee. Special thanks to John for taking time reading through the manuscript and providing technical and grammatical comments. Also thanks to Sandy Kaplan for editing this dissertation, which significantly improved its quality. I take responsibility for any remaining errors.

I would also like to thank fellow graduate students: Melanie Fulgham, Jack Lo, Terrance Goan, Kurt Partridge, Brendan Mummy, and Derrick Weathersby, for sharing frustrations, helping with presentations, and teaching me English.

My appreciation also goes to the technical staff of the Computer Science Laboratory and the administrative staff of the Computer Science and Engineering Department, most notably, Frankye Jones. Their assistance in the backstage has eased my use of the computer systems and my dealings with the University bureaucracy.

Finally, I want to thank my parents for their unconditional love and for inspiring me to come studying in America. Although at times I frowned upon their over-detailed plan for my career and future, I have to admit the outcome of the plan has always been rewarding.

The work presented in this dissertation was supported by grants from the National Science Foundation.

Xiaohan Qin

December, 1997

## Chapter 1

#### INTRODUCTION

The design of medium-scale shared-memory multiprocessors has been influenced by two recent trends. The first is using clusters of processors as basic building blocks. The second trend is using programmable protocol processors and software for maintaining cache coherence. This thesis concerns with performance issues arising from employing software cache coherence in cluster environments. Our goal is to evaluate the overhead of a software scheme and investigate ways to reduce the software overhead through either simple hardware assists or software means.

#### 1.1 Motivations

During the last decade, advances in semiconductor technology have contributed stead-fastly to the shrinking of transistor size and the speeding of clock rates. The performance of microprocessors has benefited greatly from the resulting increase in real estate and clock speed. At the same time, the amount of data generated by personal computers, workstations, and other high-speed electronic devices has increased enormously. The flourishing internet is connecting more and more computers. Inexpensive and immediate accesses to the global network have motivated both consumers and producers to use more online processing and services, e.g., electronic newspaper/publishing and electronic commerce. To provide competitive products or high quality services, raw computing power is not sufficient. Commercial and government institutions must find ways to deal with the growing volume and use of data.

The demand for powerful and scalable enterprise-wide computing resources is at a premium.

In the enterprise server market, bus-based shared-memory multiprocessors, or multis [11], have already enjoyed a tremendous success. Many computer vendors ship their servers in this form, e.g., IBM's PowerPC-based RS/6000 J40 and J50 multiprocessor servers and HP's PA-RSIC-based 9000 K-class servers connecting up to six processors. Despite its success, the single-bus system has a major drawback: It can only accommodate a small number of processors because the bus soon becomes an overcommitted resource. This lack of extensibility due to bus contention is exacerbated by the fact that processor speed increases faster than the corresponding growth in bus bandwidth and reduction in memory latency.

One way to expand the number of processors without sacrificing the shared-memory paradigm is to consider each multi as a cluster node and to link nodes using an interconnection network such as a mesh [41] or a SCI ring [43]. The cluster architecture is more scalable than the single-bus multiprocessor for two reasons. First, the number of links or the aggregated bandwidth of the interconnection network can grow as cluster nodes are added to the system. Second, shared resources in each node, e.g., the bus, memory, and the I/O node, serve only a small number of processors; they are distributed in the system.

There exists a wide spectrum of implementations based on the shared-memory programming model, from tightly coupled hardware-based cache-coherent schemes (DASH [41], Alewife [2], Origin [39], and Exemplar [14]) to software-based shared-memory systems. Some of the latter rely on page management mechanisms in the operating system to fault on illegal accesses (IVY [42] and Treadmarks [4]). Others exploit compiler analysis techniques to detect stale data in cache [65, 17, 32]; another group modifies the program's executable to perform cache consistency checking before accessing each shared variable (Blizzard-S [57], Shasta [56]).

This dissertation studies a class of cluster architectures that employs communi-

cation processors and software to implement fine-grain cache coherence protocols, similar to those of DASH. In the DASH prototype, cache coherence is maintained at two levels. Within a cluster node, the caches of individual processors are kept coherent via a snoopy bus protocol. When a memory reference cannot be resolved by the intra-cluster snoopy protocol, it is intercepted by the communication/memory management unit (CMMU), which connects the cluster to the network and maintains inter-cluster cache coherence using a directory-based protocol.

Many systems with an interconnect [41, 2, 39, 14] implement the communication/memory controller in hardware as ASIC logic. The hardware-based CMMU usually includes a limited set of functions, e.g., a high-performance messaging mechanism (optimized for small messages), a fixed protocol, and, perhaps, some prefetching capability [41]. Most optimizations geared at reducing the communication cost, such as protocol improvements and weak consistency memory models, require non-trivial hardware modifications. Furthermore, the rigidity of the hardware scheme prevents the protocol policies and optimizations from being adapted to the needs of a given application.

Recent developments in shared-memory multiprocessor systems have led many computer architects to advocate using programmable protocol processors rather than ASIC to provide basic communication mechanisms and using software to enforce cache coherence policies. Efforts in that direction include Flash [38, 28] at Stanford, s3.mp [49, 48] at Sun Microsystems, Typhoon [55] at Wisconsin, and more recently NUMA-Q [43] at Sequent. The biggest advantage of software cache coherence is its flexibility and extensibility. Multiple protocols can be easily incorporated in one system. Additional functions may be obtained by programming the protocol processor. Furthermore, while a hardware full-map directory scheme limits the number of nodes in a system, a software scheme avoid such limitations, because the data structures for maintaining cache coherence are software-based.

This flexibility, however, comes at a cost in performance, since one can always

build a hardwired controller that outperforms the software scheme for any given protocol. Software overhead can diminish performance in two ways. First, it directly contributes to the longer latency of some memory transactions (e.g., remote memory accesses) that require services from the protocol processor. Second, since the protocol processor is shared by several compute processors, the high service demand for the unit makes it a potential bottleneck of the cluster node.

This dissertation investigates ways to make use of the flexibility of protocol processors to provide users with some advantageous features of asynchronous message-passing, or explicit communication primitives, that hide memory latency with computation. Our study is performed in three phases. First, we study via trace-driven simulations the overhead of software cache coherence schemes and the performance gain of the programmer/compiler-controlled communication primitives in an architecture whose cluster node contains a single compute processor. This simplifying architectural assumption lets us isolate the effect of software overhead from that of shared resource contention. Second, we develop an analytical model to assess contention on shared resources such as the communication processor, the bus, memory, etc. The analytical approach allows us to search a large design space and identify quickly the architectural configurations worth further investigation. Finally, we evaluate in cluster environments the software implementation of the base cache coherence protocol as well as the software implementation enhanced by the communication primitives.

#### 1.2 Contributions

This dissertation makes the following contributions to the study of cluster architectures that employ communication processors and software to maintain cache coherence.

• We proposed a set of explicit communication primitives to be executed on the protocol processors. These primitives can be used by the programmer or com-

piler writer to provide hints that enable the memory system to place data where they are needed. We demonstrated with examples and simulations the use and performance of the communication primitives in an architecture with a single compute processor per cluster node. Given the parameters that we chose for the communication processor, the memory latency of the software solution is at least 50% higher than that of the hardware implementation. With communication primitives, the optimized software scheme approximates, and sometimes exceeds, the hardware solution's performance in the simplified "cluster" architecture.

- We developed a model based on Mean Value Analysis (MVA) [40, 67] to assess the contention on cluster-shared resources and to estimate the impact of contention on the overall performance of normal cluster architectures. We used the model to evaluate a number of architectural choices, i.e., varying cluster size and adding simple hardware support (remote cache and forwarding logic) to ease contention. The analytical model indicates that the base software implementation of cluster architectures can outperform the single bus system. However, unless an application has good cluster locality, increasing cluster size often harms performance, due to the high software protocol processing overhead. The remote cache can improve performance significantly; it is most effective for applications suffering primarily from capacity or conflict misses. For applications that have a large portion of coherence misses, forwarding logic is more important. We validate the analytical model against simulation results and show that the accuracy of our model is within 5-30% of simulation results.

- We investigated the performance of communication primitives in cluster environments. We found results similar to those of uni-processor node implementation. However, when the cluster size increases, the memory overhead reduction brought by the communication primitives decreases because the growing native

intra-cluster data sharing deceases the utility of the primitives. The remote cache is very important to communication primitives even when applications suffer mainly from coherence misses. The forwarding logic is crucial to communication primitives that require the processing of many small requests.

### 1.3 Organization of the Thesis

The remainder of this thesis is organized as follows. Chapter 2 describes the base architecture and its major components and discusses design and implementation issues. Chapter 3 introduces the communication primitives absent from a pure cache coherent shared-memory scheme. The goals of the chapter are to assess: (1) the overhead of software-based cache coherence protocol, and (2) the performance benefit of the communication primitives in an architecture where there is abundant hardware, hence little contention over shared resources. Chapter 4 develops an MVA-based analytical model for estimating the contention on shared resources. With the fast and reasonably accurate evaluation technique, we evaluate a number of architectural choices, i.e., varying cluster size and adding additional hardware. We also validate the model against simulation results. Chapter 5 studies the performance of communication primitives in cluster architectures. We then examine the effects of three architectural choices (discussed in Chapter 4) on the performance gain achieved by the communication primitives. Finally, we summarize the thesis and propose future work in Chapter 6.

## Chapter 2

## ARCHITECTURAL FRAMEWORK

This chapter, describes the baseline architecture, its major components, and the two-level cache coherence protocol. The cluster architecture employs two-split transaction devices: the interconnection network and the split transaction bus. These shared resources cause complications in implementing a cache-coherent shared-memory, which this chapter also addresses. Finally, we discuss issues involved in software implementation of a directory protocol.

### 2.1 Baseline Architecture and Components

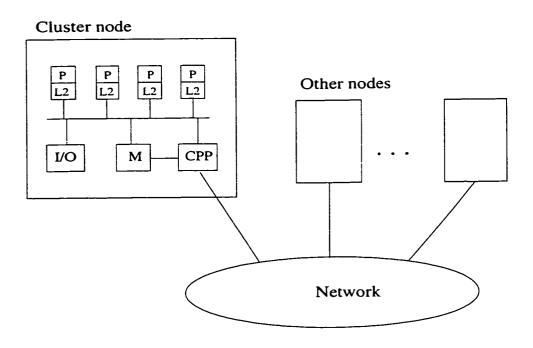

Our study is based on an architecture consisting of clusters connected to each other by an interconnection network such as a mesh (Figure 2.1). Each cluster is a bus-based shared-memory multiprocessor augmented with a communication processor (CPP). The communication processor replaces the hardwired CMMU; it performs under software control the functions of the directory protocol. Every processor has a private cache (or cache hierarchy). Cache coherence is maintained at two levels. Within a cluster node, a snoopy protocol keeps the local caches coherent. Across cluster nodes, a directory-based protocol tracks the caching information and maintains coherence on a cache-line basis. To achieve a high bus bandwidth, we assume that data and addresses use separate split transaction buses. Our machine model is CC-NUMA, which has a global physical address space; each piece of data is assumed to live in only one of the memory modules, i.e., the data's home node. Furthermore, we assume that memory is sequentially consistent.

The remainder of this section examine three components of the cluster architectures: the communication processor, the memory and its access path, and the interconnect. Our interest in the network chiefly pertains to its performance.

Figure 2.1: Model of the cluster architecture.

#### 2.1.1 Communication Processor

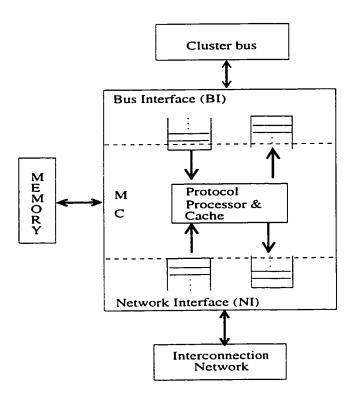

The communication processor in the base architecture, Figure 2.2, contains an embedded protocol processor (PP) for running protocol handlers, a network interface (NI) for draining/pumping messages from/to the network, a bus interface (BI) for communicating with local processors, and a memory controller (MC) that lets the protocol processor access memory. The BI and NI each have two queues. The input queue of the BI stores requests and replies from the compute processors, e.g., miss requests and writeback data. It will also be used to save user-initiated communication primitives as we expand the functions of the protocol processor (discussed in Chapter

Figure 2.2: Model of the communication processor.

3). The output queue of the BI stores replying data and invalidation/writeback requests, etc. The input and output queues of the NI store the same types of messages from/to another node.

Handling small messages is one of the most critical functions of the communication processor. Therefore, we employ an integrated memory-mapped network interface for the CPP. We also believe that the messaging mechanism should be flexible enough to accommodate system evolutions. As a result, we chose to use interrupts to notify the embedded protocol processor of message arrivals and to schedule and dispatch messages in software based on their priorities. This is different from MAGIC, a customized communication co-processor in FLASH [38], which executes both message scheduling and dispatching in specialized hardware. The motivation for our choices is that the types and formats of messages may change as the system evolves. The

versatile interrupt and software dispatching mechanisms let the system easily adjust to such changes. Interrupts were chosen over polling (the NI and BI) to free the communication co-processor from the overhead involved in periodical message checking. As we shall see in Section 3.2, this is important when we extend protocol processor functions to lower-priority execution of communication primitives.

When an arriving message interrupts the protocol processor, the interrupt handler dispatches the message to an appropriate message handler based on its type. The message handler either executes the message directly or moves the message from the BI or NI to a software message queue. To handle an interrupt efficiently, we require a processor architecture to have at least one hardware contexts dedicated to the message-receiving interrupt handler and cache coherence handlers. Thus, the service for interrupts and the cache coherence messages always avoids the overhead of register saving and restoring.

#### 2.1.2 Memory and Its Access Path

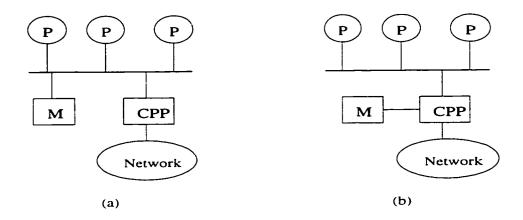

Memory usually stores data and instructions for the compute processors. In the software cache coherence scheme, it also contains the local memory's directory accessed by the protocol processor exclusively. There are two possible ways to design an access path to memory. One is to attach the memory directly to the shared bus (Figure 2.3a). This design lets local memory references bypass the communication processor. On the other hand, it puts a stringent timing constraint on the communication processor: if a memory block is not in a desired state, the CPP must intervene in the ongoing memory operation by performing a fast lookup of the memory state. In hardware-based cache-coherent systems, such as DASH, the directory access cycle can be designed to match that of the main memory. For a software cache coherence scheme, however, it may not be possible to complete the memory state lookup (in software) in time to abort the illegal memory operation. A plausible solution, employed in STiNG [43], is to add SRAM that stores the memory state and performs

snoopy operations in hardware. The SRAM controller can easily meet the timing constraint to detect and intercept requests to invalid memory blocks.

Figure 2.3: Choices of memory access path.

An alternative is to connect the memory to the communication processor (Figure 2.3b). In this case, all references that cannot be satisfied by the local caches go through the communication processor. Both hardware and software implementations of the directory protocol are feasible without the additional SRAM to store the memory state. For example, in Alewife [2], when a cache miss is encountered, the CMMU (hardware directory logic) first looks up the directory state; it then either issues a memory read if the block is in a clean state or a writeback if the data have been modified. The s3.mp [49] implementation is similar, except that both the state lookup and cache coherence are performed by microcode running on the protocol engine.

The memory design in our architectural model lies between these two alternatives (see Figure 2.1). We first assume that applications can distinguish shared data references from private data references. For private references, the memory can supply data without consulting the CPP on memory state. For this purpose, then, the memory module is directly connected to the shared bus. For shared references, the memory is prevented from answering the bus request directly; the communication

processor is always involved in looking up the memory state and supplying data, if necessary. This design avoids using costly SRAM and slowing down private data references. It also saves on memory otherwise needed to store the protocol states for private data. However, if a thread migrates from one processor to another, its private pages should be purged from the cache. The protocol processor may need to access the memory to obtain directory information or data if they are not in its own cache. To avoid having the PP contend with compute processors for the shared bus, we employ a dedicated link between the CPP and memory.

Since private and shared data accesses can be distinguished, we require for private accesses that only read misses block the compute processor; write misses use write buffers. For shared references, we require that both read and write misses and write hits to shared lines block the compute processor. For write operations, the processor cannot proceed until all other nodes have acknowledged the invalidations sent on behalf of the write. Since private references are important to the issuing processors only, how they interleave with references from other processors dos not affect the execution of other processors. Therefore, the overall memory system is guaranteed to be sequentially consistent.

#### 2.1.3 Interconnection Network

Two important metrics gauge the performance of interconnection networks: bandwidth and latency. One way to measure the aggregate bandwidth  $(B_{total})$  is to consider the total data transfer rate of all channels<sup>1</sup>. By definition, it is a product of the number of links  $(L_{total})$  and the link bandwidth  $(B_l)$ . Assuming that data are transferred on only one of the clock edges<sup>2</sup>, then  $B_l = ClockRate \times BitWidth$ . Ob-

<sup>&</sup>lt;sup>1</sup> Alternatively, one can measure aggregate bandwidth by the bisection bandwidth. Bisection bandwidth is the maximum data rate between two halves of a network, which is a product of link bandwidth and the number of links that sever a network into two equal halves.

<sup>&</sup>lt;sup>2</sup> Some networks can transfer data on both edges of the clock [44, 69].

viously, the wider the link, the larger the link bandwidth. For this reason, many high performance networks employ parallel data links [23, 61, 26, 13, 44]. Suppose an end-to-end message traverses h hops on average, the effective bandwidth available to a cluster node is approximately  $B_{total}/(h \times n) = (B_l \times L_{total})/(h \times n) = B_l \times k/h$ , where n is the total number of nodes in the system and  $k = L_{total}/n$  is the number of links per node.

Examples of high-performance networks for tightly coupled parallel systems are Caltech's Mesh Routing System [23] (whose variations have been used in Paragon [31], DASH [41], and Alewife [2]) and IBM's Vulcan Switch [61] (used in SP1 and SP2 [70, 3]). Table 2.1 presents the performance data for two networks: DASH's 2-D Mesh Routing Chip (or MRC) and SP's MIN Vulcan Switch.

Table 2.1: Network performance data for DASH and SP2.

|                                 | Mesh Routing Chip | Vulcan      |

|---------------------------------|-------------------|-------------|

|                                 | used in DASH      | used in SP2 |

| Nodes                           | 16                | 16          |

| Clock rate (MHz)                | 28.5              | 40          |

| Bitwidth of data link (bits)    | 16                | 8           |

| Link bandwidth (Mbits)          | 456               | 320         |

| Aggregate bandwidth (Gbits)     | 58                | 41          |

| Bandwidth per processor (Mbits) | 910               | 853         |

| Mean number of hops (nodes)     | 4                 | 3           |

| Switch and wire delay (ns)      | 50                | 75          |

| Average network delay³(ns)      | 200               | 225         |

<sup>&</sup>lt;sup>3</sup> The average network latency given in Table 2.1 does not include network interface latency.

It is worth noting that although the high-performance networks used in prior parallel systems are proprietary, they are becoming commodity parts. For example, the NUMA-Q [43] employed SCI (Scalable Coherent Interface) [26] to connect multiprocessor cluster nodes. The basic topology of SCI is a ring, in which the output of one SCI node is connected to the input of the downstream node. In the ring topology, a SCI node performs very simple functions. It either removes incoming packets whose destination id matches the node id or passes packets to the next node. The simple functionality and point-to-point style connection make it possible to achieve a very high clock rate. For example, the SCI switches manufactured by Vitesse Semiconductor Corporation run at 500MHz. However, the bandwidth available to each processor is only  $2 \times B_t/n$  (k = 1 and h = n/2). As the number of clusters (n) increases, the effective bandwidth per processor decreases quickly, and the average message latency increases linearly. To increase the bandwidth, multiple rings or higher dimension topologies may be necessary.

#### 2.2 Cache Coherence Protocols

As mentioned earlier, cache coherence in a cluster architecture is maintained at two levels. Cache coherence within a cluster node is enforced via a snoopy protocol. Across clusters, cache coherence is maintained by a directory-based protocol. This section describes the detailed operations of these protocols and specifies the interface between them.

#### 2.2.1 Intra-cluster Snoopy Protocol

In a snoopy cache coherence protocol, a cache line can be in one of five states<sup>4</sup> [62]:

<sup>&</sup>lt;sup>4</sup> The EXCLUSIVE state suggests that the data live in one and only one cache. A write hit to an EXCLUSIVE line is performed without issuing any bus request. The OWNERSHIP state indicates that the memory does not have valid data for the block. The cache that owns the line

- 1. M (MODIFIED): Exclusive and owned

- 2. O (OWNERSHIP): Non-exclusive but owned

- 3. E (EXCLUSIVE): Exclusive but not owned

- 4. S (SHARED): Non-exclusive and not owned

- 5. I (INVALID)

If classified by cache state, the Write-once and Illinois protocols [6, 62] each have four states (M, E, S, and I) and therefore belong to the family of MESI protocols. The Berkeley protocol [6, 62], on the other hand, is a member of MOSI.

The EXCLUSIVE state in a stand-alone bus-based multiprocessor is easy to implement: all processors snoop on the shared bus, and each can observe all memory transactions. In a cluster architecture, this is no longer the case. When a processor requests a line to share, the request is seen on the bus of the requesting node and, possibly, on the bus of the home node. The home node must contact the node with an EXCLUSIVE cache line and request it to change the line to a SHARED state. Because of this extra overhead, we decided to use a MOSI protocol.

Our protocol is a variation of the Berkeley protocol. The main differences are twofold. First, our protocol enables more cache-to-cache transfers. For example, the Berkeley protocol only lets the owner of a line, i.e., the cache line in MODIFIED or OWNERSHIP state or the memory, supply the data. Our protocol lets SHARED lines respond as well. Second, our protocol defines the interface between intra-cluster and inter-cluster protocols. More specifically, when a memory request cannot be satisfied in a cluster node, the intra-cluster protocol generates a message of a specific type for the inter-cluster directory protocol. We describe the operations of our intra-cluster snoopy protocol as follows. The message's type is given in italics.

Read miss: If the line is MODIFIED, OWNERSHIP, or SHARED in the cluster, one

of the local caches supplies the data. A MODIFIED is changed to OWNERSHIP. If

is responsible for updating the memory, if necessary, when it replaces data.

none of the local caches has the data, a *ReadMiss* message is generated and entered into the communication processor. After the request is serviced, the block is loaded into the cache (of the requesting processor) in a SHARED state.

- Write hit: If the line is MODIFIED, the write proceeds with no delay. Otherwise, the line must be SHARED or OWNERSHIP<sup>5</sup>. If the cluster has the ownership, it is transferred to the requesting processor after the local copies are invalidated. Otherwise, an ObtainOwnership message is generated and entered into the communication processor. After the request is completed, the state of the cache line is set to MOD-IFIED.

- Write miss: If the line is MODIFIED or OWNERSHIP<sup>5</sup> in one of the local caches, the cache supplies the data and grants ownership after the local caches invalidate their copies. If the line is SHARED in the cluster, the local caches invalidate their copies, one of them supplies the data, and an ObtainOwnership is generated and entered into the communication processor. If none of the local caches has the block, a WriteMiss message is generated and entered into the communication processor. After the request is serviced, the block is loaded into the requesting processor's cache in a MODIFIED state.

### 2.2.2 Inter-cluster Directory Protocol

The intra-cluster protocol generates an explicit message for the inter-cluster protocol when a memory reference request cannot be satisfied by the former. In the directory protocol, a memory block can be in one of three states, MODIFIED, SHARED, and UNCACHED. In addition to the state, the directory keeps a complete list of

<sup>&</sup>lt;sup>5</sup> When a cache line is in the OWNERSHIP state, the line may be shared by other caches in the same cluster, but not by caches in any other clusters. The memory block must be in the MODIFIED state in the directory (cf. Section 2.2.2). Therefore, no inter-cluster invalidation is generated.

nodes that may have a copy of the block. From the directory's viewpoint, nodes are clusters, not individual processors. When the protocol processor receives a memory reference request (i.e., a message of ReadMiss or ObtainOwnership or WriteMiss) from the bus interface, it first determines the home node based on the address, and, if appropriate, forwards the request to the home node. At the home node, the protocol processor looks up the state of the memory block and performs operations as follows.

- ReadMiss: If the memory block is SHARED or UNCACHED, the protocol processor reads data from memory and sends it to the requesting node. If the memory block is MODIFIED, the protocol processor looks up the node that modified the block and requests that the node write back the data. As the data arrives, it is forwarded to the requesting node and written back to memory. The directory state of the block is set to SHARED.

- ObtainOwnership: The memory block must be SHARED. The home node sends

invalidations to all nodes sharing the line except the requesting node. After receiving

all the acknowledgements, the home node grants ownership to the requesting node.

The directory state is set to MODIFIED.

- WriteMiss: If the memory block is UNCACHED, data are read from memory and sent to the requesting node. If the memory block is SHARED, the home node sends invalidations to all nodes sharing the line. Also, data are read from memory. Upon receiving all the acknowledgments, the data and ownership are sent to the requesting node. In both cases, the state of the memory block becomes MODIFIED. If the block is MODIFIED, the protocol processor requests that the owner write back and invalidate the line. After the data arrives, the data and ownership are granted to the requesting node. The directory state of the block is still MODIFIED.

## 2.3 Cache Coherence and Split Transaction Devices

In a shared-memory system, two processors may request access to a piece of data at the same time. If both requests are reads, the order in which they are executed is unimportant. However, if one request is a read and the other is a write, the system must guarantee that one request is executed before the other for the sequential consistency model is to be maintained. In a system that relies heavily on split transaction devices, e.g. the split transaction bus and the interconnection network, a memory operation and the cache coherence protocol are carried out as a sequence of sub-operations. Maintaining the order of two memory operations can be tricky in certain circumstances. This section explores issues involved in maintaining memory operation ordering on split transaction devices. We then discuss the network properties required by directory-based protocols.

#### 2.3.1 Memory Operation Ordering

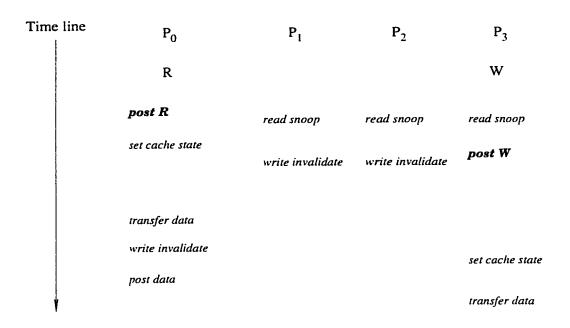

Memory operations are executed as a sequence of sub-operations. Sub-operations such as cache snooping and response are executed in parallel by multiple devices. For the cache coherence protocol to function correctly, the sub-operations of two conflicting memory accesses should appear to be in the same order. In other words, the sub-operations of one memory request are executed in the same order with respect to the sub-operations of another memory request on each device. For example, suppose  $P_0$  encounters a read miss R at the same time as  $P_3$  encounters a write miss W to the same address. R is granted service first. Obviously,  $P_0$  cannot perform the invalidation on behalf of  $P_3$ 's write before transferring the data for the prior read. Figure 2.4 depicts the correct ordering of sub-operations for two conflicting memory requests:

In a stand-alone bus-based multiprocessor, memory sub-operation ordering can be enforced by the bus arbitrator and by the FIFO queue in each bus device

Figure 2.4: Memory sub-operation ordering.

that stores the coherent transactions received from the bus. If two processors raise concurrent requests, the requests' sub-operations enter the FIFO in the order granted by the bus arbitrator. The FIFO queue guarantees that the sub-operations of one request are executed before the sub-operations of the other request on each respective device. Furthermore, the scheme ensures that the two requests are completed in the same order as they were issued to the bus.

This approach is unnecessarily conservative: if two concurrent requests reference independent locations, their sub-operations need not follow the bus arbitration order strictly. A more sophisticated implementation that can relax the sub-operation ordering of two independent memory accesses is to remove long latency pending sub-operations (such as memory reads) from the FIFO queue and store them in a small fully-associative cache buffer. The subsequent sub-operations match their addresses to those of the pending sub-operations in the cache before being executed. If there is no conflict, they can proceed; otherwise, they can be retried later.

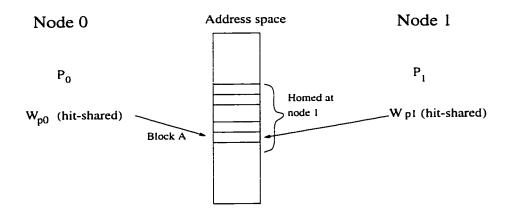

In a cluster architecture, the preceding optimization becomes more important, since a pending memory reference could take a few hundred cycles to complete. However, if the bus devices simply hold the addresses of pending requests, they may cause deadlock. To explain why deadlock can occur, let us look at the situation in Figure 2.5. In the scenario,  $P_0$  in Node 0 issues a request to write  $(W_{p0})$  a shared line A. The request is intercepted by the communication processor and forwarded to home Node 1. Before receiving  $W_{p0}$ , the home node receives another request from  $P_1$  of Node 1 to write to the same line  $(W_{p1})$ . In servicing  $W_{p1}$ , the home node sends invalidations to clusters sharing the line, including Node 0. Because  $W_{p0}$  is still pending, if  $P_0$  holds the invalidation of  $W_{p1}$ , a cyclic dependence is formed:  $W_{p1}$  cannot carry on because  $P_0$  is holding the address for  $W_{p0}$ . Meanwhile,  $W_{p0}$  cannot continue because the home node is guarding the line for  $W_{p1}$ .

Figure 2.5: A deadlock-prone scenario.

We know that if a memory operation O cannot be resolved within a cluster C, it enters into the communication processor. While the request is pending, two kinds of conflicts can occur: (1) a local compute processor raises a read or write miss request  $(O_1)$  to the same address, or (2) a communication processor (home node) issues a writeback or invalidation request  $(O_2)$  to the same line. These two cases

must be handled differently. In the former case, since the operation of O can affect the snoopy result of  $O_1$ ,  $O_1$  should retry. In the latter case, the fact that  $O_2$  arrives at node C while O (from node C) is still pending implies that the home node issues  $O_2$  prior to processing O; therefore,  $O_2$  should take precedence, and O should retry.

# 2.3.2 Directory Protocol and Network Properties

Since the directory protocol frequently uses the interconnection network, the behavior of the network affects to a great extent the implementation of the directory protocol. This section lists the network properties required by a directory protocol and states our assumptions that simplify protocol implementation.

Reliability. Although the directory protocol can be implemented on unreliable interconnection networks, the implementation would be complicated and incur significant overhead if every outgoing message needed to be saved in order to recover from network errors. In most high-performance interconnects, however, data links usually operate under a well-controlled environment and span only a few meters. Therefore, the occurrences of bit errors or lost packets are extremely rare. Even if transmission errors do occur, networks such as Mercury [69, 44] and S-connect [47] provide reliable network service through hardware retransmission. Hence, in our study, we assume a reliable interconnection network layer.

In-order delivery. Under the sequential consistency memory model, correct operation of the directory-based protocol depends not only on a reliable network layer, but also on in-order message delivery. To elaborate, suppose node A issues a request to share a memory block, which is to be serviced by home node H. Meanwhile, node B issues a write request to the same line. At home node H, B's write arrives after A's read. As a result, H sends the replying data first to A, then an invalidation on behalf of B. If the invalidation arrives at A before the data does, node A would have an erroneous cache state. Even in networks that guarantee in-order message delivery, the split transaction style of memory accesses is still vulnerable to thrash-

ing situations under extreme conditions, which can happen more easily in systems adopting multithreading processors. Kubiatowiz [37] illustrated several scenarios of "vulnerable windows" and discussed a range of solutions to the problems<sup>6</sup>.

Deadlock. Interconnects such as Caltech's Mesh Routing Chip [23] are guaranteed to be deadlock free if messages are consumed at their destination. Problems arise when this condition is not satisfied due to the limited number of buffers in the network interface. To sink the messages and clear the network interface buffers as quickly as possible, designers usually prioritize messages based on their demand on network resources and their chances of causing deadlock. Acknowledgements or replying data are often given higher priorities, because processing them usually does not consume network resources, and their completion helps remove pending requests and release other resources. But message prioritization only reduces the likelihood of deadlock; it does not eliminate the problem. In case deadlock does occur, the system may have to drop messages in order to move forward. To avoid this complication, our study assumes that the network interface has sufficiently large input queues to sink messages.

# 2.4 Software Implementation of the Directory Protocol

We next discuss issues and details pertaining to the software implementation of a directory protocol. These include directory memory management, message handlers, and cache replacement.

# 2.4.1 Directory Memory Management

The coherence directory data structure we use is the dynamic pointer scheme [58, 38]. Each memory block has a directory header and a linked list of shared nodes. The

<sup>&</sup>lt;sup>6</sup> These solutions are beyond the scope of our thesis, and the author refers you to [37] for further information.

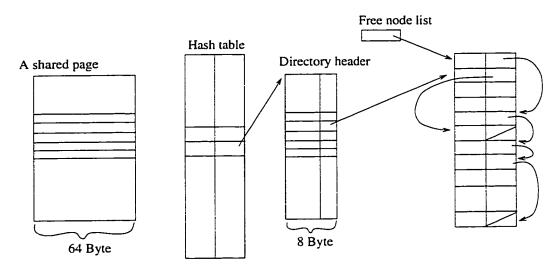

directory header saves the state of the memory and the pointer to the shared node list. The directory headers of a (shared) page are organized as an array, an entry in which corresponds to one cache line-size memory block (Figure 2.6). The memory overhead of the directory header array is a function of the size of the directory header and the size of a cache line. Suppose the directory header is 8 bytes and the cache line size is 64 bytes, a 4KB page then needs a directory header array of 0.5KB, or 12.5% overhead.

Figure 2.6: Coherence directory data structures.

Memory for the directory header array is allocated dynamically from a free directory-header-array pool. A hash table maps the physical address of a shared page to the address of a directory header array. When a shared page is referenced for the first time, the mapping is invalid. At that time, a directory header array is allocated, and a map is established for that page. Subsequent accesses to blocks in this page find the directory header array by a hash lookup and the directory header of a specific block by adding a displacement. Note that the communication processor does not recognize virtual addresses. Only physical addresses are passed to the communication processor.

Memory for the shared node lists is also dynamically allocated from a free nodelist store. Initially, the OS assigns a certain number of physical pages (for the free directory-header-array pool and the free node-list store) to the communication processor based on the amount of memory applications request for shared data structures. This number can increase at runtime if the OS detects that it is allocating more shared pages than expected on a particular node.

## 2.4.2 Message Handlers

The protocol processor starts a message handler after receiving a message interrupt. The message handler can either process the message to completion if all coherence actions can be taken in the node or process the message partially if other nodes of the system are needed (e.g., write hit on a shared line). In the latter case, the handler needs to suspend itself, yielding control to other threads.

Before a message handler suspends itself, it sets the directory of the memory block to a transient state to prevent subsequent requests to the same line from being processed prematurely. In addition, the message handler creates a data structure to be used upon receiving the expected messages. This data structure contains the handler's name and state (indicating a point where the handler should continue once the expected messages arrive), a pointer to the directory header of the memory block in progress, and necessary bookkeeping information, e.g., the number of acknowledgements received. To resume the suspended handler appropriately, the replying messages carry a pointer to this data structure. During execution of the message handler, interrupts are disabled, as in Active Messages [68].

#### 2.4.3 Cache Replacement

Cache replacement can cause instantaneous inconsistency between the directory information and the cache states. Inconsistencies occur between the time a node sends

a request for replacing a cache line and the time the home node processes the request. Such inconsistency complicates implementation of the directory protocol. Consider the situation in which a home node requests a block to be written back from node  $C_1$ . The data are in MODIFIED or OWNERSHIP state in processor  $p_1$  of  $C_1$ . Before  $p_1$  receives the writeback request, it replaces the same line and sends the modified data to the home node while the home node is waiting for a reply to its writeback request. When the writeback request actually arrives at  $C_1$ , the data would no longer exist in the node. Consequently,  $C_1$  sends a negative acknowledgement (Nack), containing no data, to the home node. When this happens, the home node can be certain that the modified data must have arrived earlier than the Nack, because the network provides in-order delivery service (cf. Section 2.3.2). The home node must preserve the data sent back by cache replacement so that it can retrieve the data when processing the Nack.

In case a line in the SHARED state is replaced, there are two options. The first is to replace the line without notifying its home node; the other is to report the replacement to the directory. The former case causes directory information to be inaccurate with respect to the state of the cache; the directory protocol can still function correctly, however. The penalty is that home nodes may generate needless invalidation messages. In the latter case, the processor that replaces the *last* shared copy in a cluster node needs to inform the home node. To do that, the bus signaling must have a capability similar to that of the snoopy protocol supporting the EXCLUSIVE state. Our implementation uses the second approach.

#### 2.5 Summary

This chapter described the base cluster architecture and its major components, i.e., the communication processor, the memory, and the interconnection network. In addition, we outlined our intra- and inter-cluster cache coherence protocols. Since the

cluster architecture relies heavily on split transaction devices, we also examined issues vital to both hardware and software implementations of a cache-coherent shared-memory. Finally, we discussed the issues unique to software implementation of the directory protocol.

# Chapter 3

# COMMUNICATION PRIMITIVES IN UNI-PROCESSOR NODE ARCHITECTURES

Although the use of communication processors and of software cache coherence permits protocol optimization and saves hardware design time, it increases the latencies of memory references that need the assistance of communication processors. This chapter addresses the memory latency problem. We propose a set of explicit communication primitives that exploit the flexibility of the programmable protocol processors. These primitives provide the user with the advantageous features of asynchronous message-passing while retaining the simplicity of the cache-coherent shared-memory paradigm.

Our goals are to assess the overhead of a software implementation of the base cache coherence protocol relative to an ideal hardware scheme and to measure performance gains when the proposed communication primitives are applied. For these purposes, we compare, via execution-based trace-driven simulation, a subset of the SPLASH-2 benchmark suite in four environments: (1) a PRAM model, (2) an idealized hardware cache coherence scheme, (3) a software scheme implementing only the basic cache coherence protocol, and (4) an optimized software solution supporting the additional communication primitives and running with applications annotated with those primitives. To isolate the effect of software overhead from that of shared resource contention, we assume in this chapter an architectural model in which each cluster node contains a single compute processor.

The rest of the chapter is organized as follows. Section 3.1 introduces the proposed

communication primitives and their semantics. Section 3.2 discusses issues involved in implementing the primitives on the communication processor. We describe our experimental methodology in Section 3.3: design of experiments, selection of benchmarks, and the simulation environment and parameters. In Section 3.4, we show how the benchmarks were modified with the introduction of the communication primitives and present simulation results of the proposed scheme and the baseline architecture. We summarize related work in Section 3.5 and conclude the chapter in Section 3.6.

# 3.1 Explicit Communication Primitives

Under usual cache coherence policies, the fetching of data is performed on demand only, i.e., when a cache miss occurs. Similarly, the storing of data in memory is done only when a replacement is needed <sup>1</sup>. The primitives that we propose extend, under programmer or compiler control, these basic data movement operations. Table 3.1 shows the primitives and their semantics. Each primitive is a non-blocking operation. Furthermore, we require that global cache coherence be maintained for the requested data.

The first two primitives, get(addr, size) and getex(addr, size), let the programmer prefetch a set of consecutive cache lines and request that these lines be either in SHARED or EXCLUSIVE state. Granting ownership to the receiving processor can significantly reduce write latency in subsequent accesses to that data. Note that the get operations are not equivalent to page migration or DMA transfers since the data are transferred to the cache of the requester and global cache coherency is maintained.

While get/getex are consumer oriented, the next two primitives, put(pid, addr, size) and putex(pid, addr, size), are producer oriented. These operations are akin to an asynchronous send in message-passing; they can be used when the producer knows the identity of the consumer. By using a put operation, the producer process can

<sup>&</sup>lt;sup>1</sup> Most of the lower-level caches in the memory hierarchy follow a write-back policy.

Table 3.1: Communication primitives. addr is the starting address of a block of data. size is its size in bytes. pid is a processor number. pids is a mask indicating a list of processors. mode is either write-back (wb) or write-through (wt).

| Primitives                  | Semantics                                     |

|-----------------------------|-----------------------------------------------|

| get(addr, size)             | fetch data into requesting processor's cache  |

| getex(addr, size)           | fetch data with ownership                     |

| put(pid, addr, size)        | place data in the cache of processor pid      |

| putex(pid, addr, size)      | transfer data with ownership to processor pid |

| multicast(pids, addr, size) | disseminate data to a set of processors       |

| putmem(addr, size)          | return data to memory                         |

| writemem(mode, addr, size)  | set the write policy                          |

store a set of cache lines, in a given state, in the cache of the processor running the consumer process. When there is more than one consumer and their identities are known, the multicast(pids, addr, size) primitive can be used.

When the producer knows that it will not use the data any longer, but does not know what process will consume it, the data can be stored in memory with the putmem(addr, size) primitive. This may save half of the request-reply bandwidth in the network when the data are next used. A similar effect can be achieved on a word-per-word basis by changing the default write-back policy to a write-through one. The writemem primitive can restrict this policy to a range of addresses; if its parameters addr and size are both null, it can be applied to all write misses. By selecting the mode, the user has the choice of alternating between the two write policies.

When utilized appropriately, these primitives benefit the application for the following reasons:

- 1. Overlap of communication with computation. This overlap can be extensive since the operations dictated by the communication primitives are non-blocking, and multiple requests can be outstanding.

- 2. Bulk data transfers. The network can be better used by pipelining transmissions.

- 3. Tailoring the cache coherence protocols. For example, superfluous data transfers present in write-update protocols can be avoided, or early requests for ownership in write-invalidate protocols can reduce the number of control messages in migratory-like patterns.

However, there are dangers in using these primitives unwisely. These dangers resemble those that exist when using prefetching or post-storing too aggressively: cache pollution, increase in coherence traffic, and saturation of the network. Therefore, the programmer or compiler writers must insert the primitives with discretion, taking into account the cache configuration and usage of the application's data.

# 3.2 Implementation Issues

The communication primitives differ from cache miss requests in four significant ways. First, the compute processor issues communication primitives directly to the communication processor without checking the state of its own cache. Second, no local snoopy operations have been performed for the lines being requested. Third, the communication primitive requests are not limited to one cache line. Fourth, they do not block the issuing processor. This section discusses the effect these differences have on the hardware and protocols and outlines our implementation strategies.

## 3.2.1 Change in Cache Controllers

Since the compute processor issues primitives without checking its own cache, the cache controller is not aware of such pending requests. Therefore, a major change that the communication primitives require from the cache controller and the bus protocol is that they allow unsolicited data to be pushed into the cache.

#### 3.2.2 Communication Primitive Protocols

Because the compute processor does not validate the requests of communication primitives with its own cache or the caches of other local processors, the protocols used for the primitives differ from those for cache miss requests. For instance, assume that a processor writes to a shared line, and the request cannot be satisfied in the local cluster; it is therefore forwarded to the home node. The home sends invalidations to all sharing nodes excluding the requesting node, because the requesting processor has already issued a local invalidation. On the other hand, if a processor issues a getex to a shared line, the home node sends invalidations to all sharing nodes including the requesting node.